# Field Engineering Theory of Operation

System/360 Model 40

Theory of Operation

Program Interrupt Multiplex Channel Selector Channel

# **Preface**

This manual describes the theory of operation of the multiplex and selector channels of the IBM 2040. It also presents the causes and effects of program interrupts and describes the operation of the interval timer.

Other manuals associated with and referenced by this publication are:

- Field Engineering Manual of Instruction, IBM System/360 Model 40, Comprehensive Introduction, Form 223-2840.

- Field Engineering Maintenance Manual, IBM System/360 Model 40, 2040 Processing Unit, Form 223-2841.

- Field Engineering Diagrams Manual, IBM System/ 360 Model 40, 2040 Processing Unit, Form 223-2842.

- Field Engineering Manual of Instruction, IBM System/360 Model 40, Functional Units, Form 223-2843.

- Field Engineering Manual of Instruction, IBM System/360 Model 40, Power Supplies, Features, and Appendix, Form 223-2845.

All three-digit figure references in this publication refer to figures in the Diagrams Manual.

The words "memory" and "storage" may be used interchangeably between this publication and the machine ALD's.

It is recommended that the user of this publication remove the staples and insert this publication in a binder with the other System/360 Model 40 instruction manuals. Major sections and items should be tabbed.

#### FOURTH EDITION

This is a reprint of 223-2844-0, incorporating changes released in the following FE Supplement:

FORM NUMBER

PAGES AFFECTED

DATE

S23-4050

30, 31, 41.1, 42, 44, 55, 69, 71, 73, 75, 81-92, 95, 96, 97.1, 101-104

November 30, 1967

Significant changes or additions to the specifications contained in this publication are continually being made. When using this publication in connection with the operation of IBM equipment, check the latest FE Publications Systems Sequence Listing for revisions or contact the local IBM branch office.

Copies of this and other IBM publications can be obtained through IBM Branch Offices. Address comments concerning the contents of this publication to: IBM Corporation, FE Manuals, Dept. B96, PO Box 390, Poughkeepsie, N.Y. 12602

# Contents

| Program Interrupts                                      | 5          | Interface Control Check                             | 60  |

|---------------------------------------------------------|------------|-----------------------------------------------------|-----|

| CPU Status with Respect to the Interrupt System         |            | Interface Parity Check                              |     |

| Stopped or Operating State                              |            | Channel Data Check                                  |     |

| Running or Waiting State                                |            | Channel Control Check                               | 60  |

| Masked or Interruptible State                           |            | Channel Timing                                      | 60  |

| Supervisor or Problem State                             | 6          |                                                     |     |

| Priority of Interrupts                                  | 6          | Selector Channel                                    | 65  |

| Machine Check Interrupt                                 | 7          | Registers                                           |     |

| Program Check Interrupt                                 | 8          | Byte Buffer (W Registers)                           |     |

| Supervisor Call Interrupt                               |            | T Register                                          | 66  |

| PRI Condition                                           |            | S Register                                          |     |

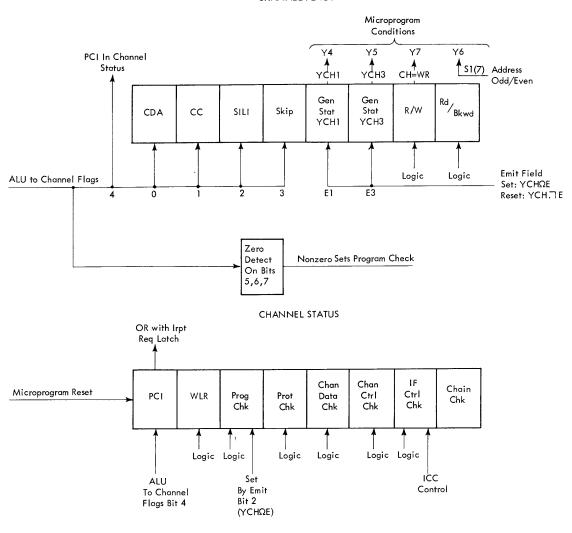

| External Interrupt                                      | 13         | Channel Flags Register                              | 72  |

| I/O Interrupts                                          |            | Channel Checks and Status Register                  | 72  |

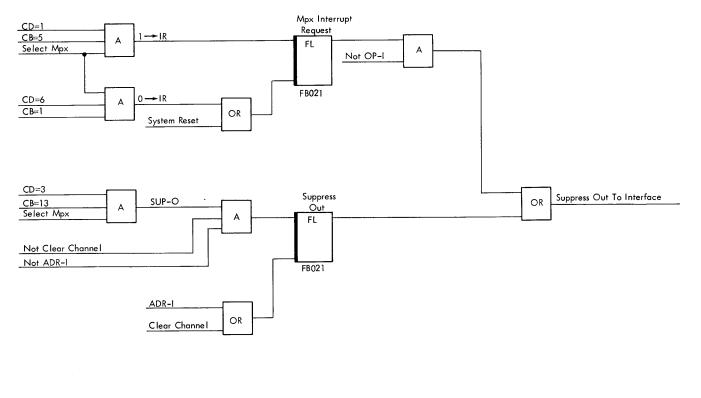

| Multiplex Channel Interrupt                             |            | Storage Protection Channel Key Register             | 72  |

| Selector Channel Interrupt                              |            | Read Only Storage Channel Address Register (ROSCAR) | 72  |

| Store PSW Microprogram                                  | 15         | Interface Controls                                  |     |

| Load PSW Microprogram                                   | 19         | Select and Hold Out Latch                           |     |

| Conditions That Set PRI but Do Not Cause a Program      |            | Unit Selection                                      |     |

| Interrupt                                               |            | Status In Tag                                       |     |

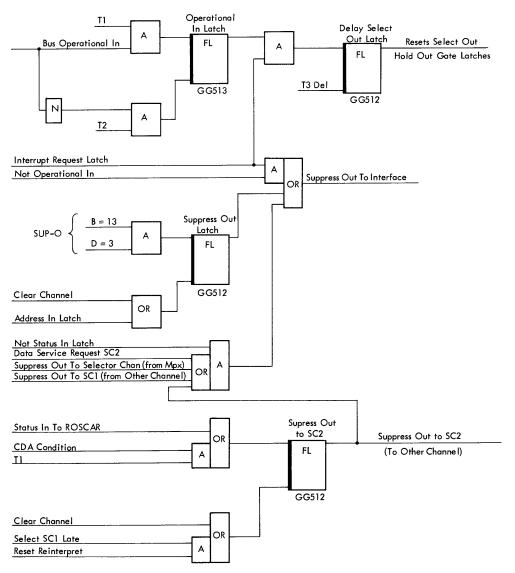

| General                                                 |            | Suppress Out to Interface                           | 76  |

| Clock Nonzero                                           |            | Channel to Channel Suppress                         | 77  |

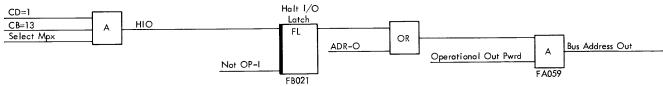

| Halt Latch                                              |            | Halt Latch                                          | 77  |

| Interval Timer                                          |            | Unit Control Word (UCW) in Local Storage            | 77  |

| Real-Time Clock                                         |            | Storage Protection                                  | 78  |

| Clock Counter                                           | 24         | Control Signal Specifications                       |     |

|                                                         |            | CB Field                                            |     |

| Multiplay Channel                                       | 05         | CC Field                                            |     |

| Multiplex Channel Selection of an I/O Device by the CPU | 25         | CH Field—LSAR Address Control                       |     |

| Channel Control Words and Formats                       |            | CJ Field—R Bus Input Control                        | 78  |

| Channel Address Word (CAW)                              |            | CL Field—R Bus Output Control                       |     |

| Channel Command Word (CCW)                              |            | CM Field—ALU Destination Control                    |     |

| Unit Control Word (UCW)                                 |            | CN Field—Stat and Function Register Control         | 70  |

| Channel Status Word (CSW)                               |            | CP Field—R Bus Input Control                        | 90  |

| Program Status Word (PSW) in I/O Operation              |            | I/O Instructions                                    |     |

| Multiplex Channel Operation                             |            | Start I/O Microprogram Test I/O Microprogram        | 00  |

| Multiplex Storage                                       | 30         | Halt I/O Microprogram                               |     |

| Storage Protection (SP)                                 | 30         | Test Channel Microprogram                           | 87  |

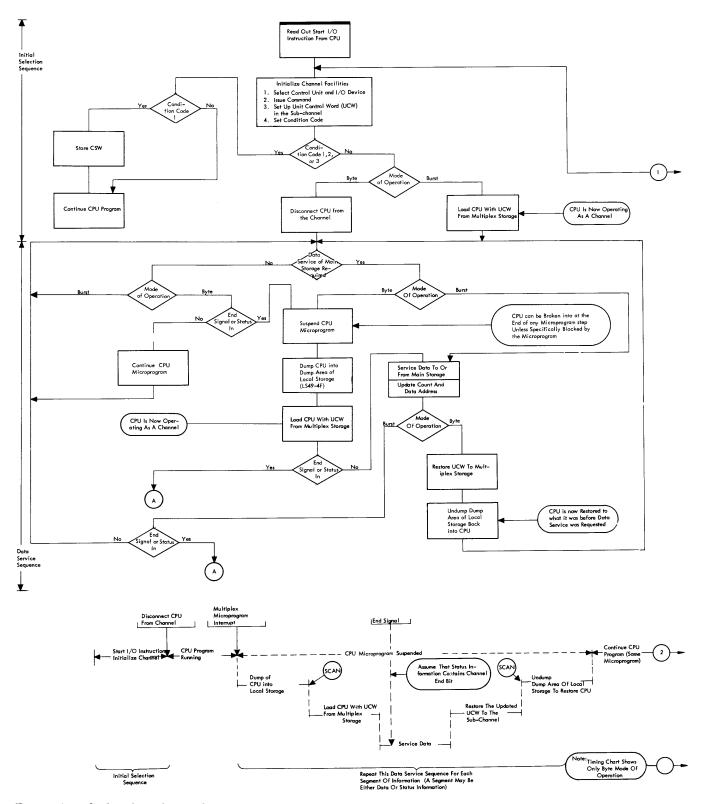

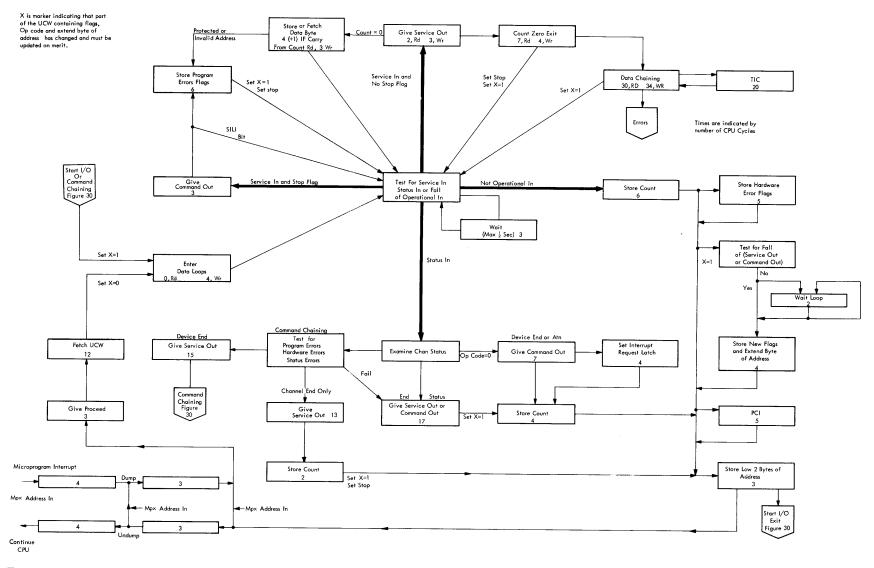

| Multiplex Channel Operation (Basic)                     | 32         | Data Servicing                                      | 88  |

| Byte Mode Operation                                     | 32         | Read                                                |     |

| Burst Mode Operation                                    | 32         | One-Byte Data Service                               |     |

| Multiplex Channel Normal Operation                      | 34         | Read Backwards                                      | 99  |

| I/O Instructions                                        | 37         | Read Skip and Backward Skip                         | 99  |

| I/O Instruction Format                                  |            | End Procedure                                       | 101 |

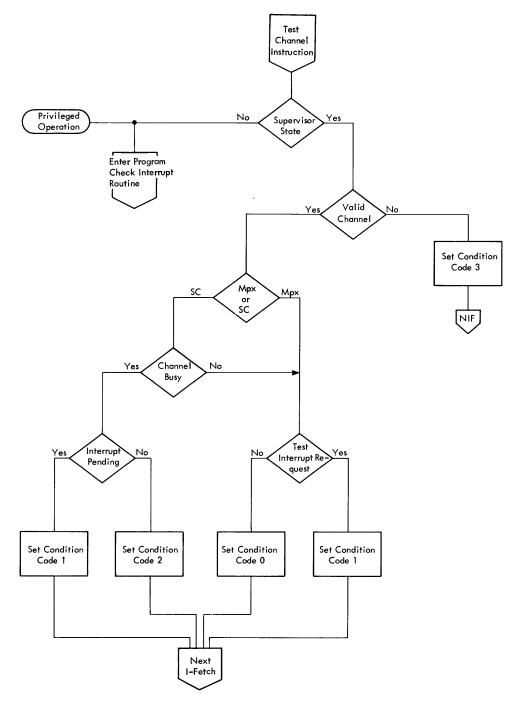

| Test Channel Microprogram                               | 37         | Write                                               |     |

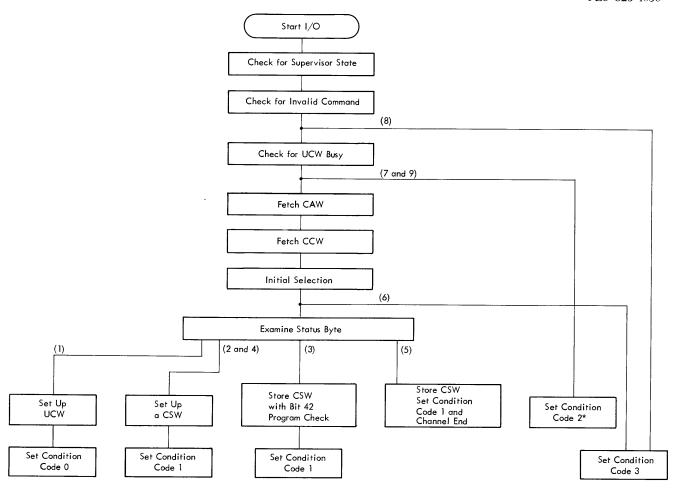

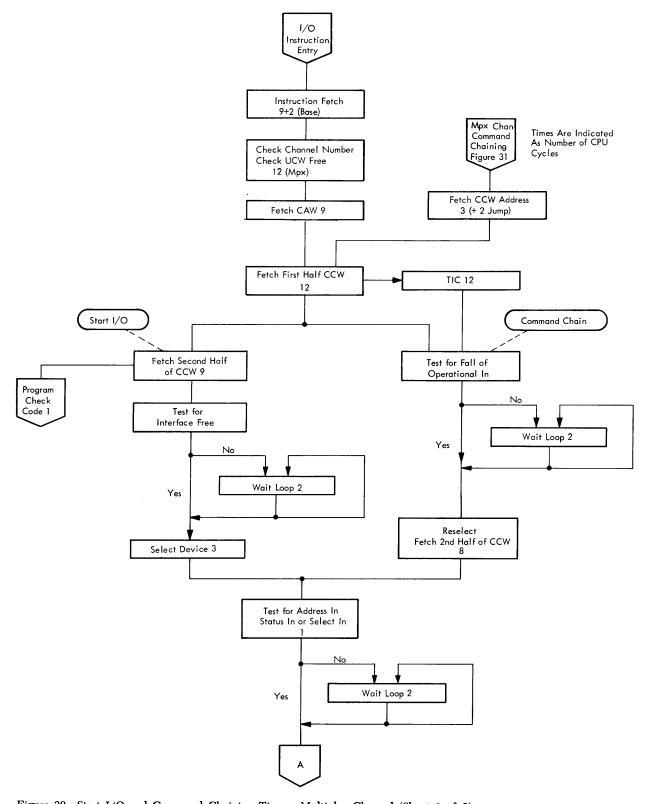

| Start I/O Microprogram                                  | 37         | Two-Byte Data Service                               | 105 |

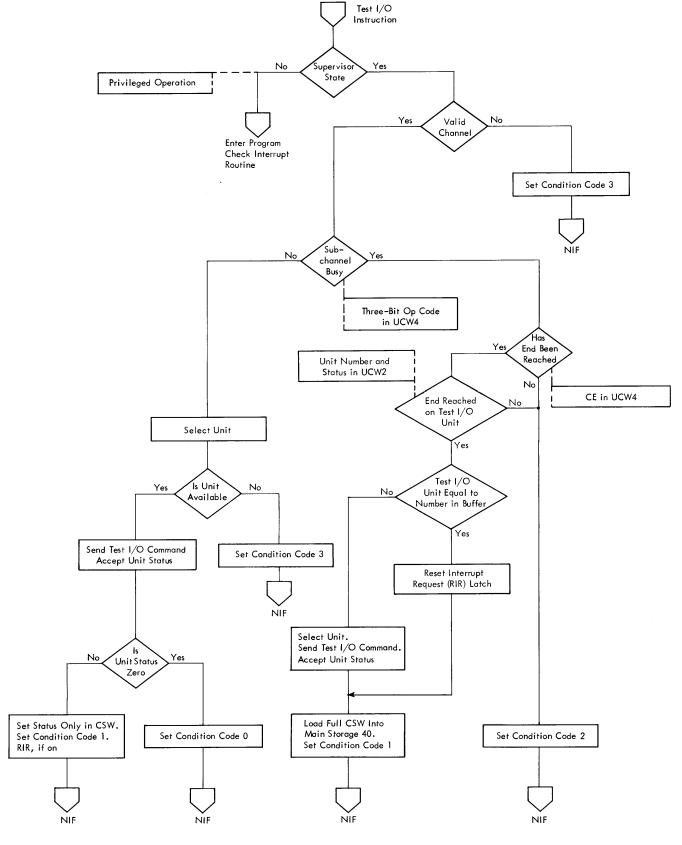

| Test I/O Microprogram                                   | 41         | One-Byte Data Service                               | 105 |

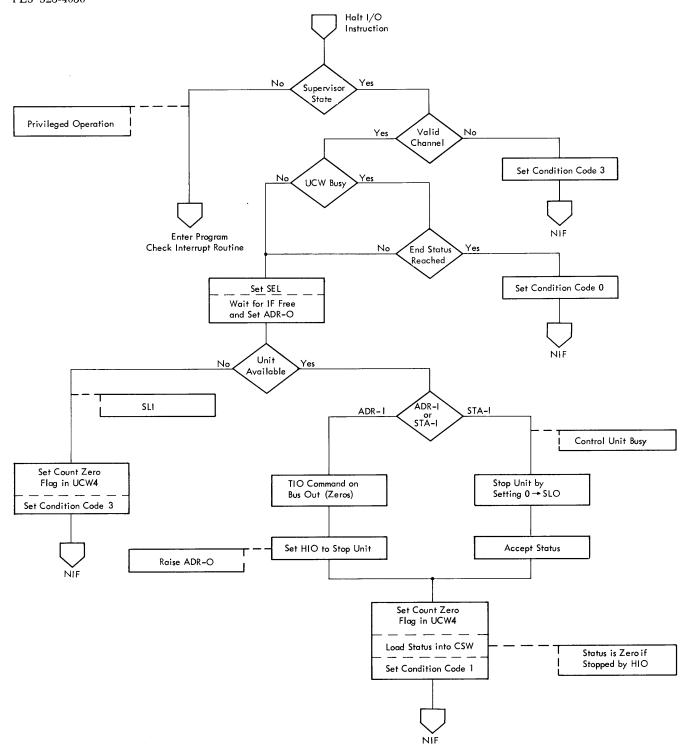

| Halt I/O Microprogram                                   | <b>4</b> 3 | Chaining                                            | 107 |

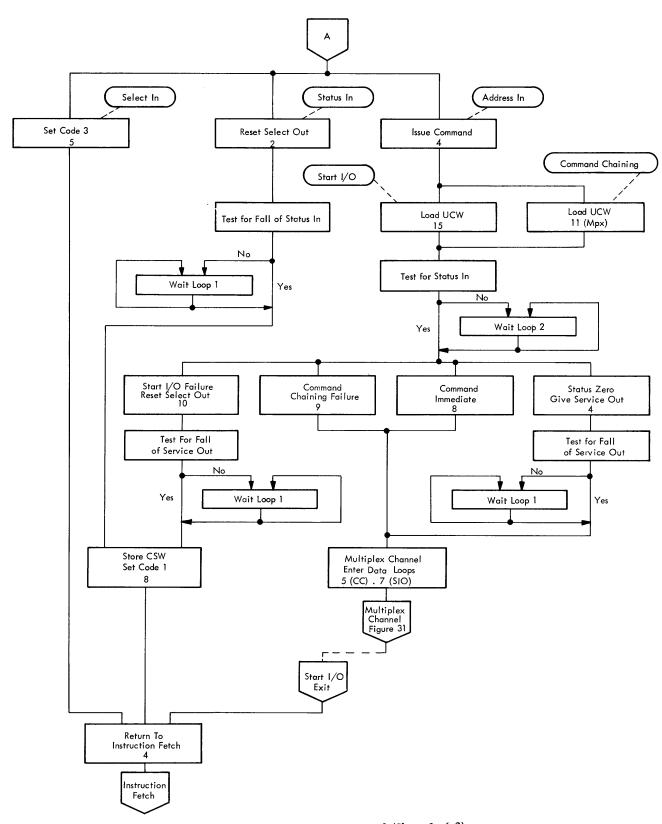

| Multiplex Channel Microprogram                          | <b>4</b> 3 | Data Chaining                                       | 107 |

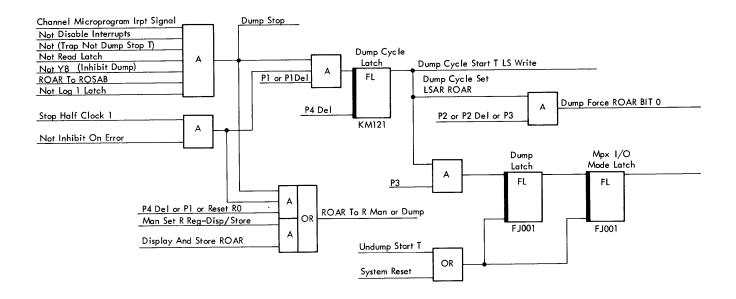

| Dump Operation                                          | 47         | Command Chaining                                    | 110 |

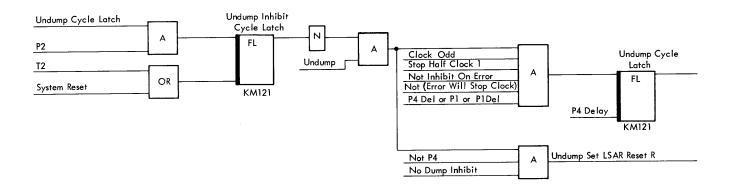

| Undump Operation                                        | 47         | Errors                                              | 110 |

| Multiplex Channel Entry from Dump                       | 49         | Multiple Tag Check                                  | 111 |

| Read/Sense Data Loop                                    |            | Buffer Data Check                                   | 111 |

| Write/Control Data Loop                                 | 50         | Any Channel Error                                   | 111 |

| Multiplex Storage Restore Microprogram                  |            | Channel Data Check                                  | 111 |

| Multiplex Error and Count Zero Microprogram             |            | IF Control Check                                    | 111 |

| Data Chaining Microprogram                              |            | Channel Control Check                               | 111 |

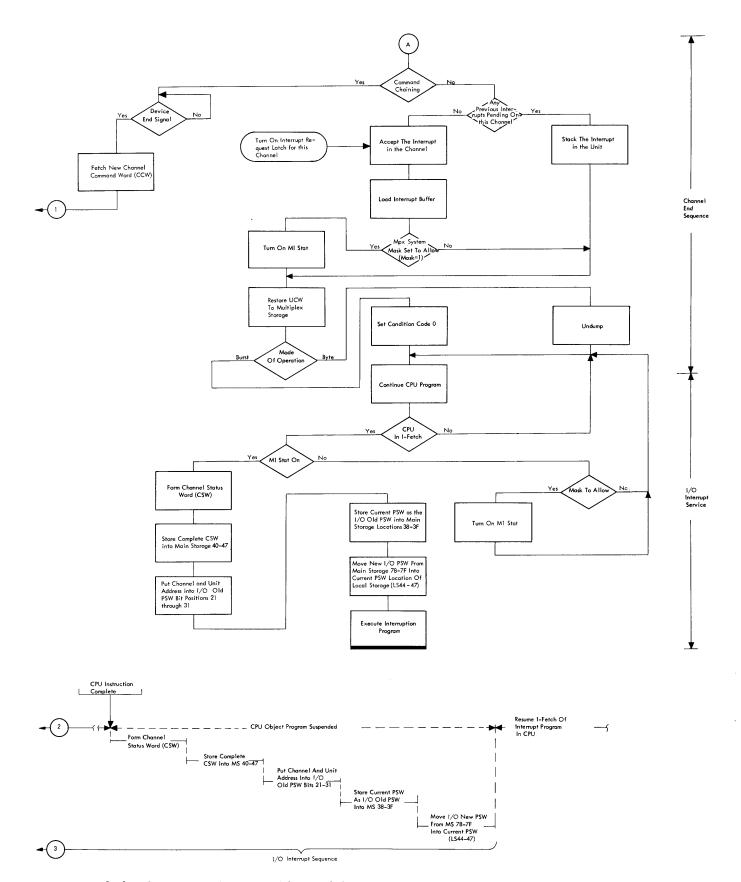

| Multiplex Channel Status                                | 52         | Chaining Check                                      | 111 |

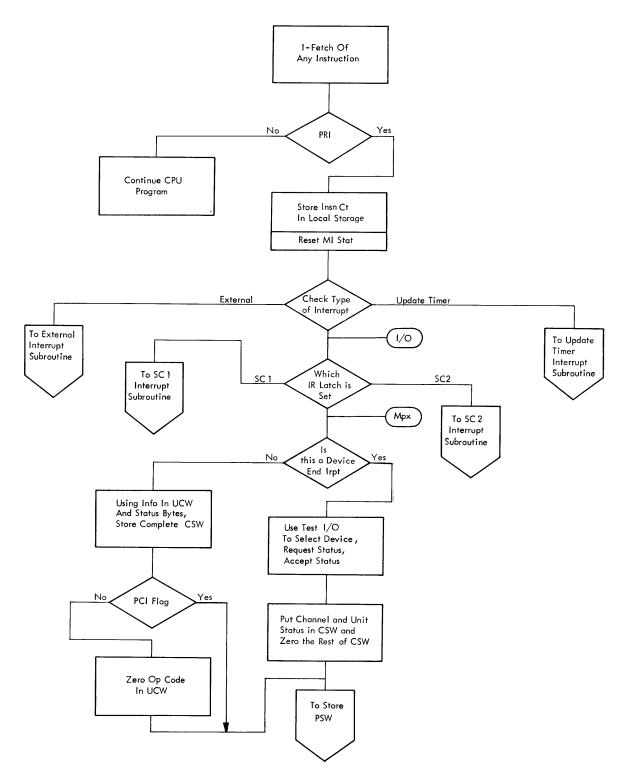

| I/O Interrupts                                          | 58         | Program Check                                       | 111 |

| End Type Interrupt                                      | 58         | Protection Check                                    | 111 |

| Device End Type Interrupt                               | 58         | Wrong Length Record                                 | 111 |

| Stacking Interrupts                                     | 60         | Interrupt Handling                                  | 111 |

| Multiplex Channel Errors                                | 60         | End Type Interrupt                                  | 111 |

| Interface Tag Check Latch                               | 60         | Device End Type Interrupt                           | 113 |

# Illustrations

| Program Interrupts |               |                                             |      | Selector Channel |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|--------------------|---------------|---------------------------------------------|------|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                    | FIGURE        | TITLE                                       | PAGE |                  | FIGURE | TITLE PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

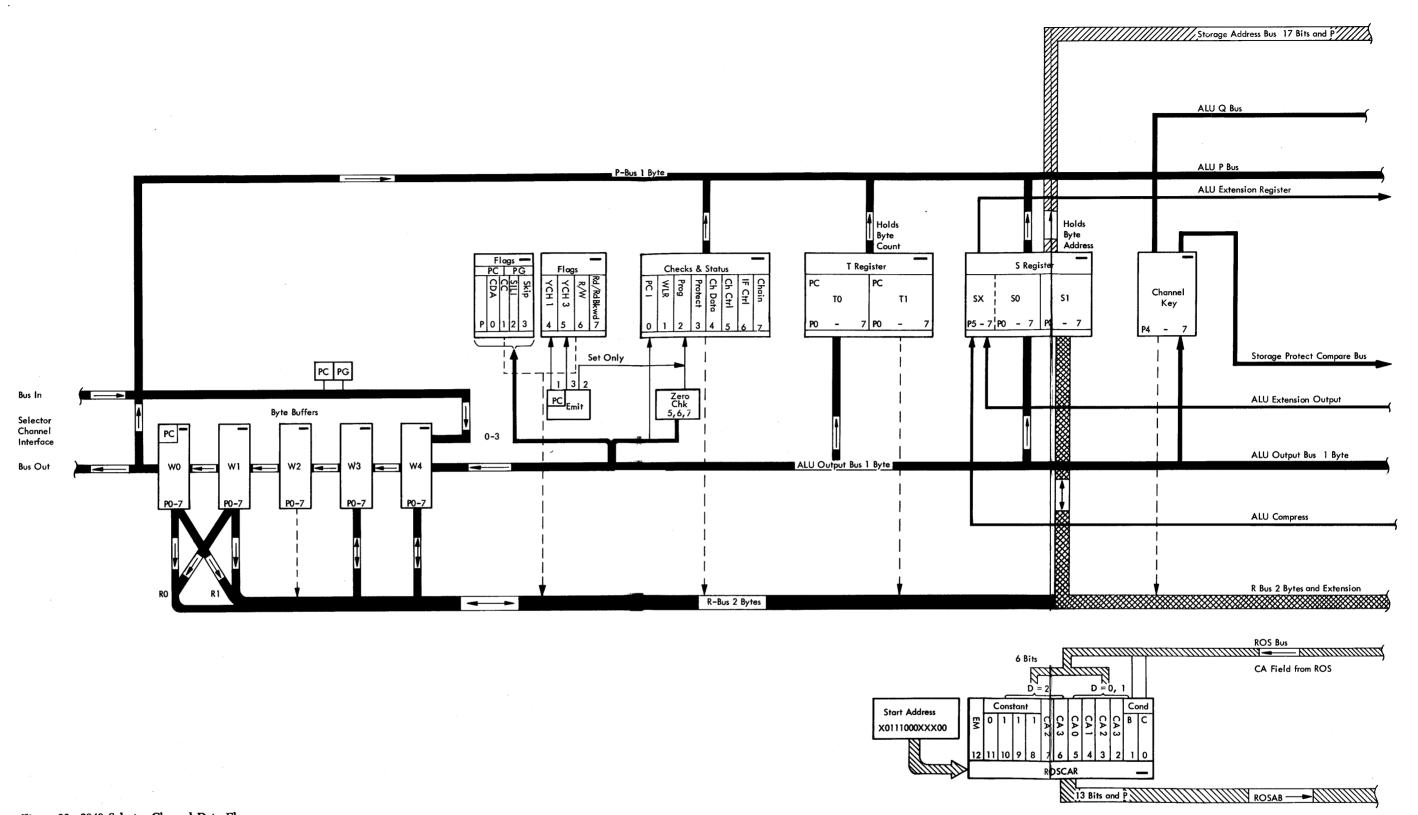

|                    | 1             | Permanent Main Storage Assignments          | . 7  |                  | 32     | 2040 Selector Channel Data Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

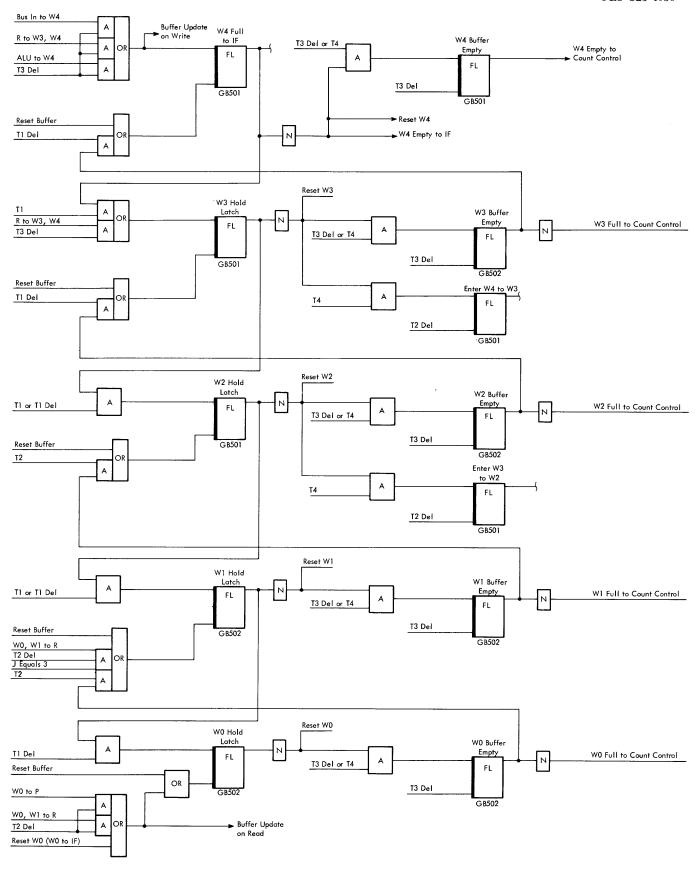

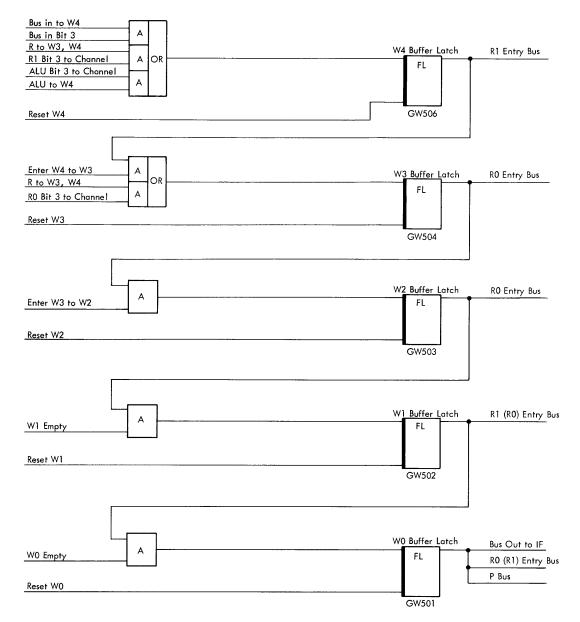

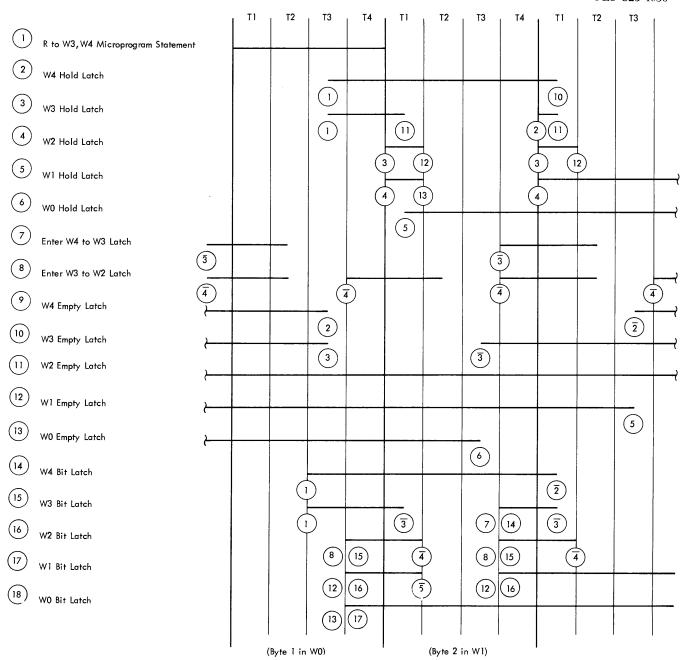

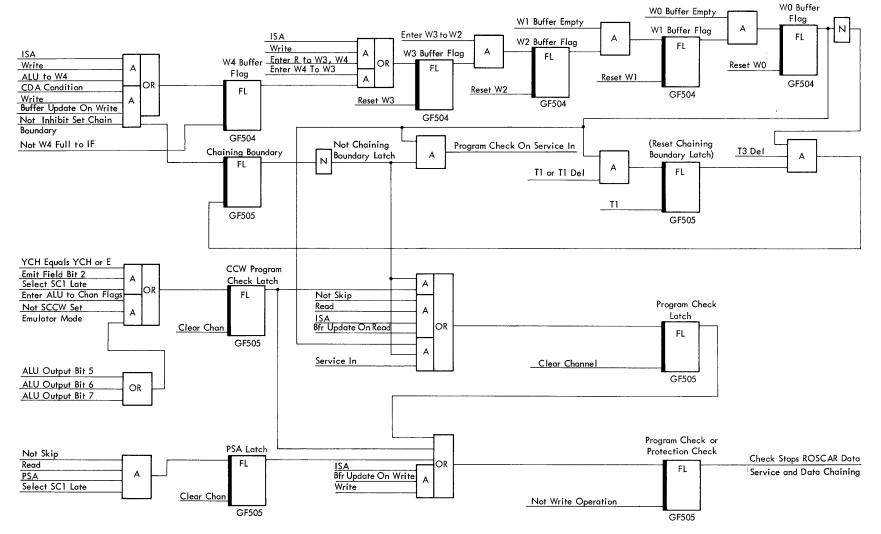

|                    | $\frac{1}{2}$ | Programming Errors                          |      | - 1              | 33     | Buffer Control Latches 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

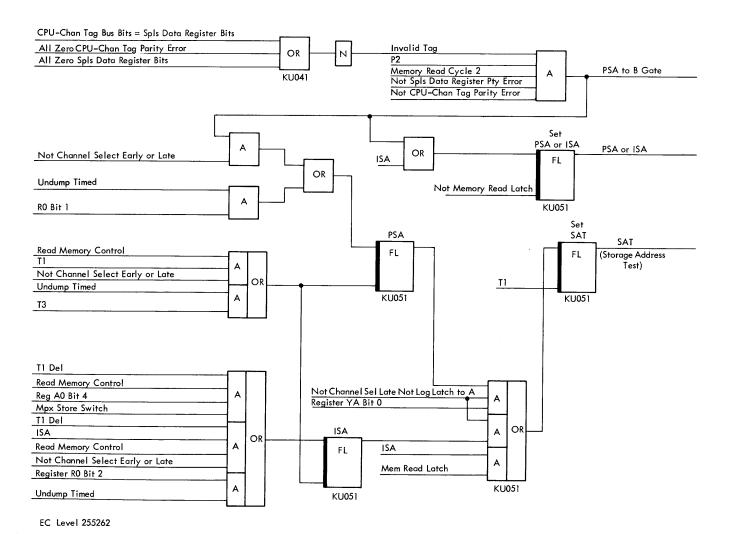

|                    | 3             | PSA and ISA Latches—SAT Condition           | . 9  |                  | 34     | W Buffer Example—Bit 370                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

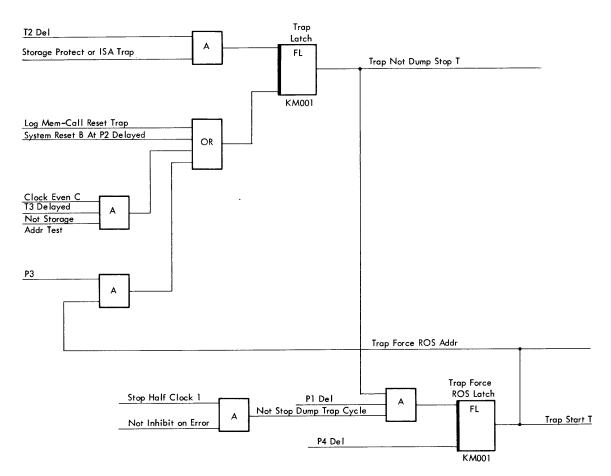

|                    | 4             | Trap Latch                                  |      | - 1              | 35     | Buffer Control—Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|                    | 5             | Trap Timing                                 |      | - 1              | 36     | Selector Channel Detail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

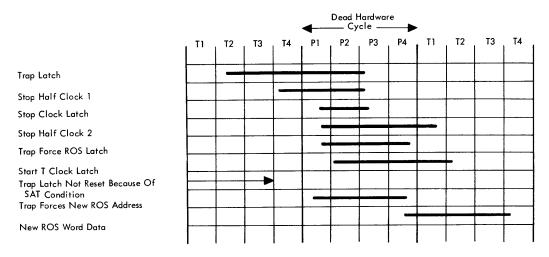

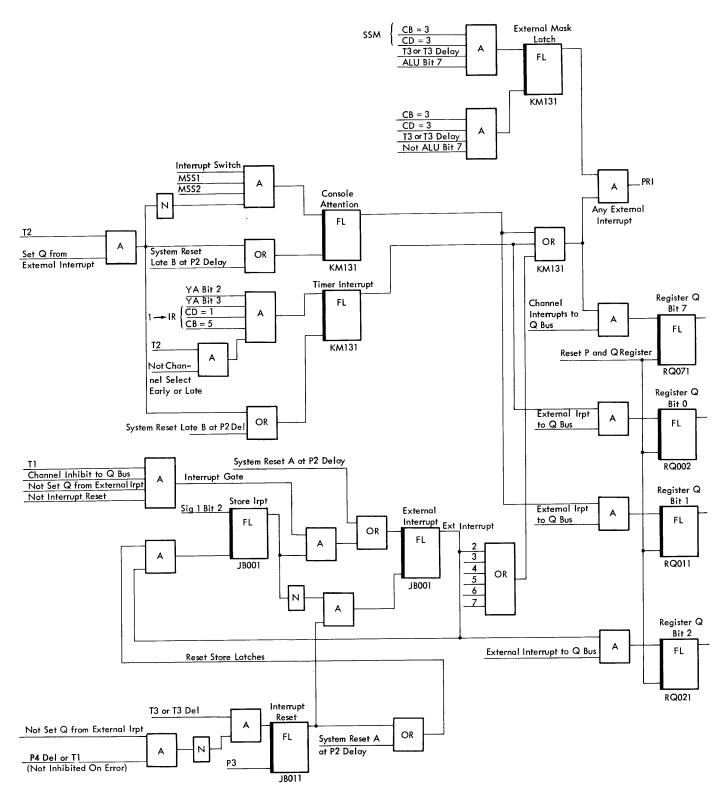

|                    | 6             | Conditions Generating PRI                   | . 12 |                  | 37     | Select Out and Interface Free 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

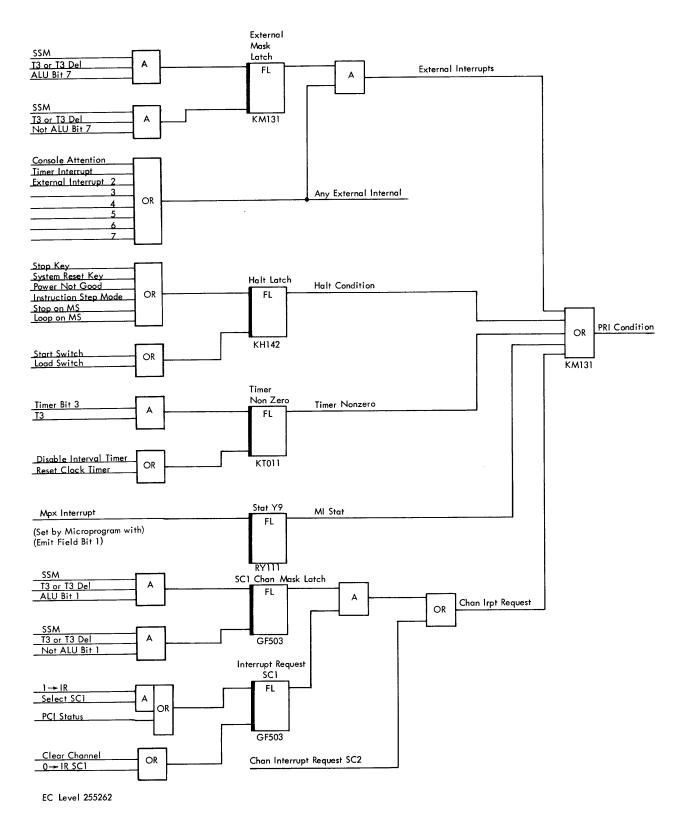

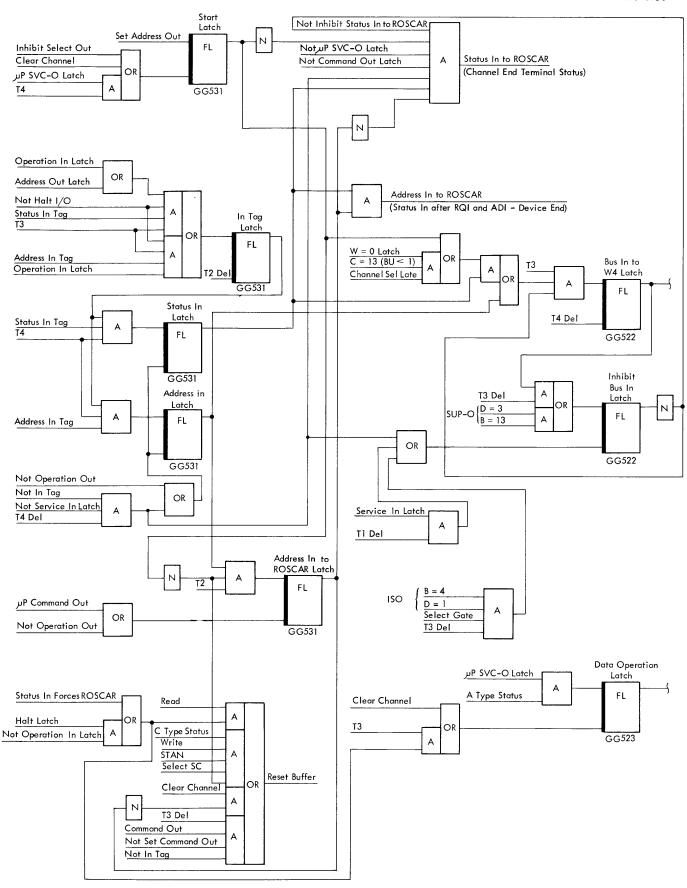

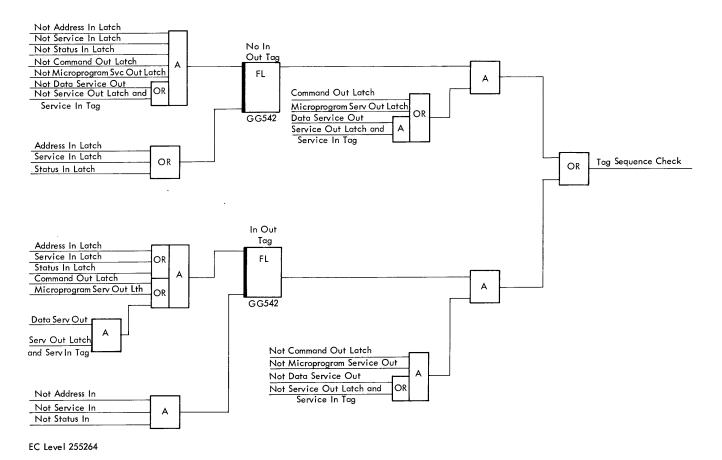

|                    | 7             | External Interrupts                         |      | 1                | 38     | In Tag System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

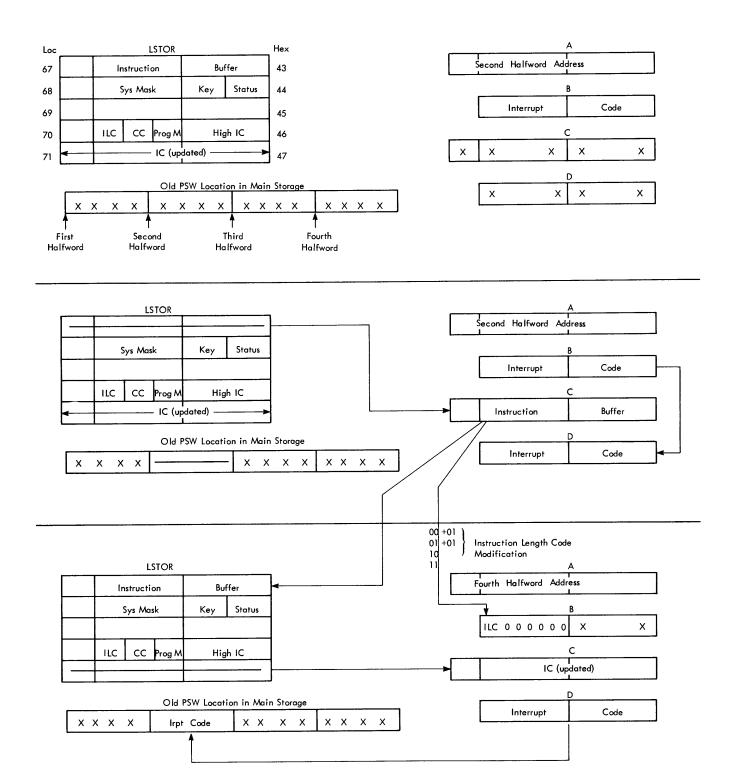

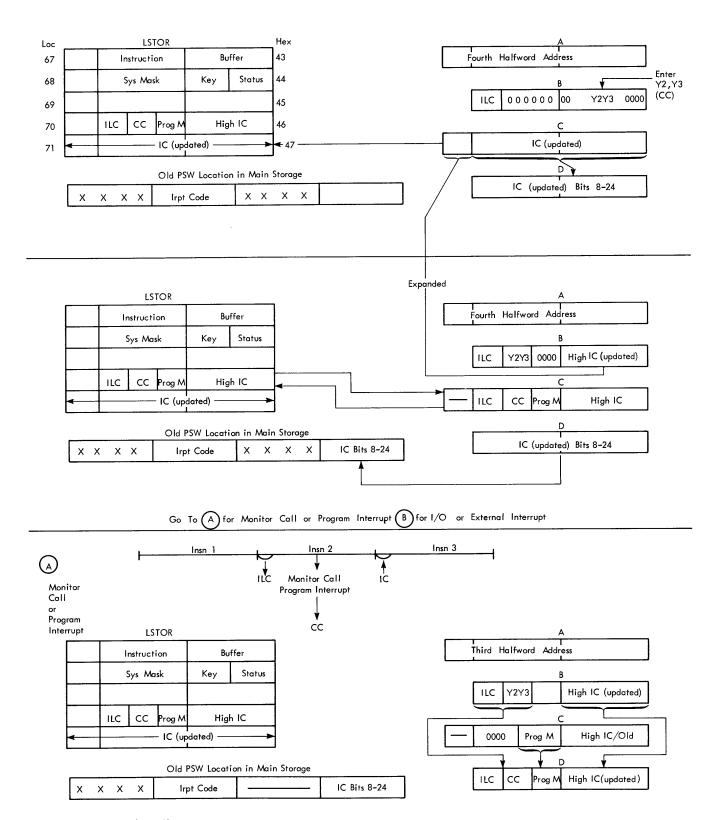

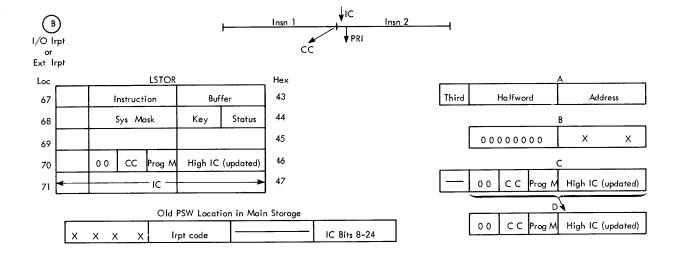

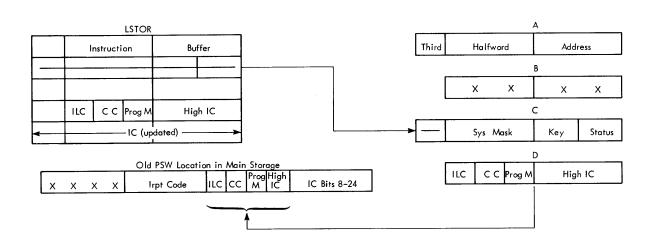

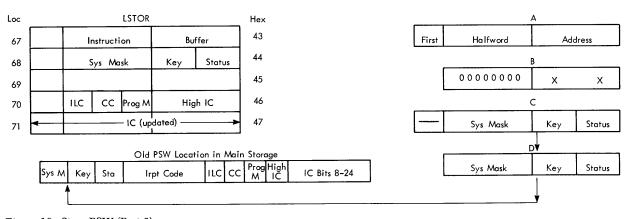

|                    | 8             | Store PSW (Part 1)                          | . 16 |                  | 39     | Suppress Out Logic SC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

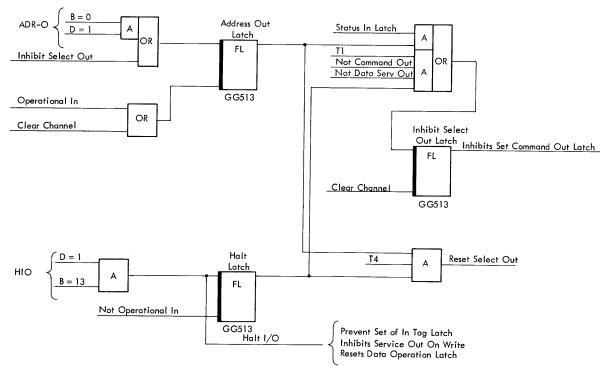

|                    | 9             | Store PSW (Part 2)                          |      |                  | 40     | Address Out Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

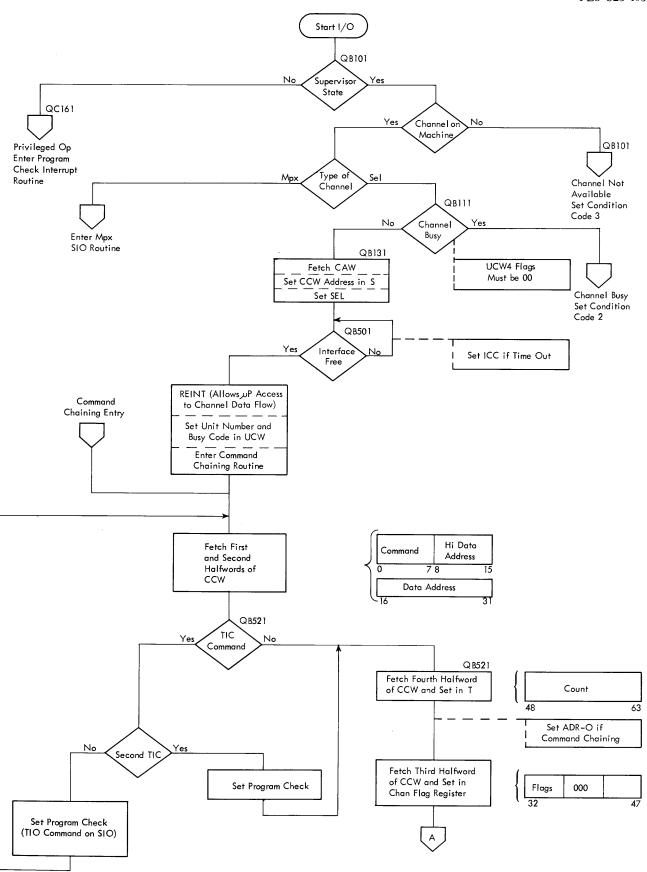

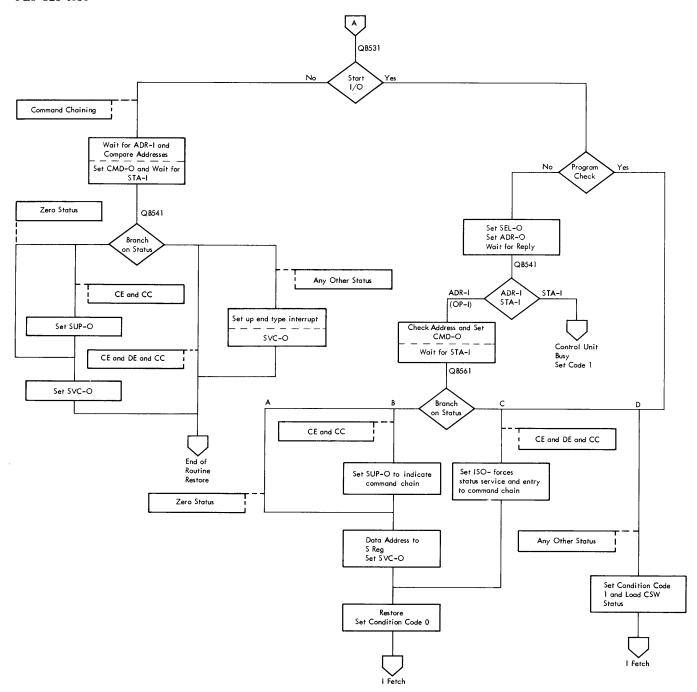

|                    | 10            | Store PSW (Part 3)                          |      | ı                | 41     | Start I/O Selector Channel (Sheet 1 of 3) 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

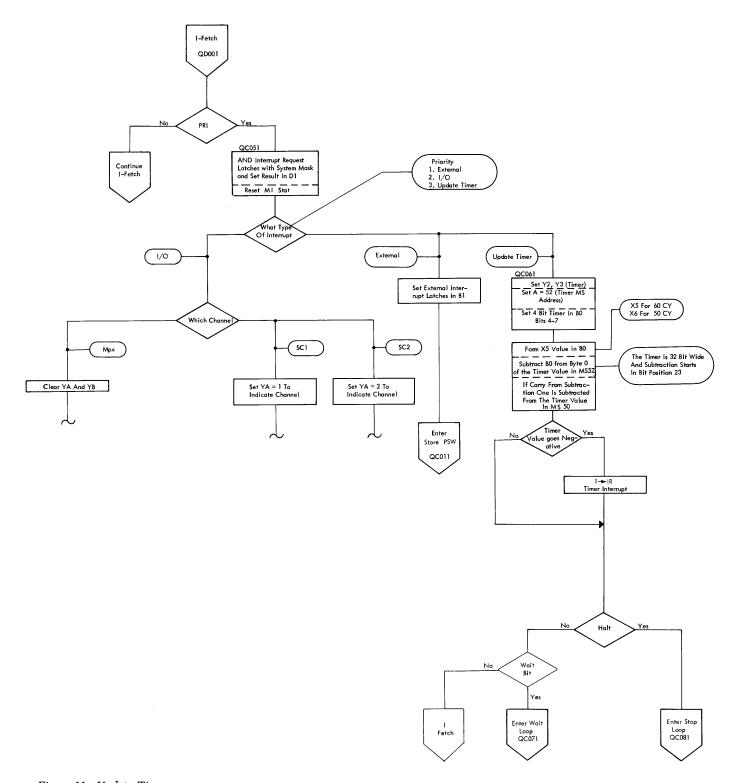

|                    | 11            | Update Timer                                | . 21 | - 1              | 41     | Start I/O Selector Channel (Sheet 2 of 3) 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                    |               |                                             |      |                  | 41     | Start I/O Selector Channel (Sheet 3 of 3) 82.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

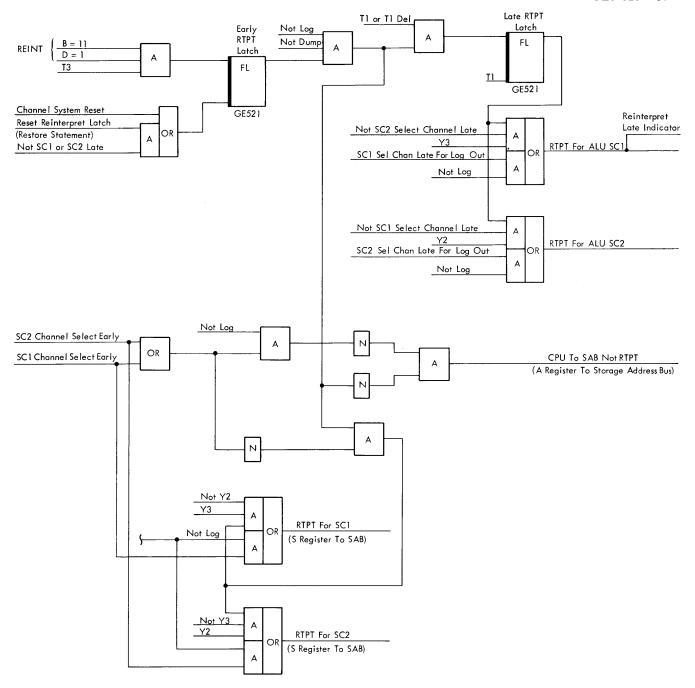

|                    | Multiple      | ex Channel                                  |      |                  | 42     | Reinterpret Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

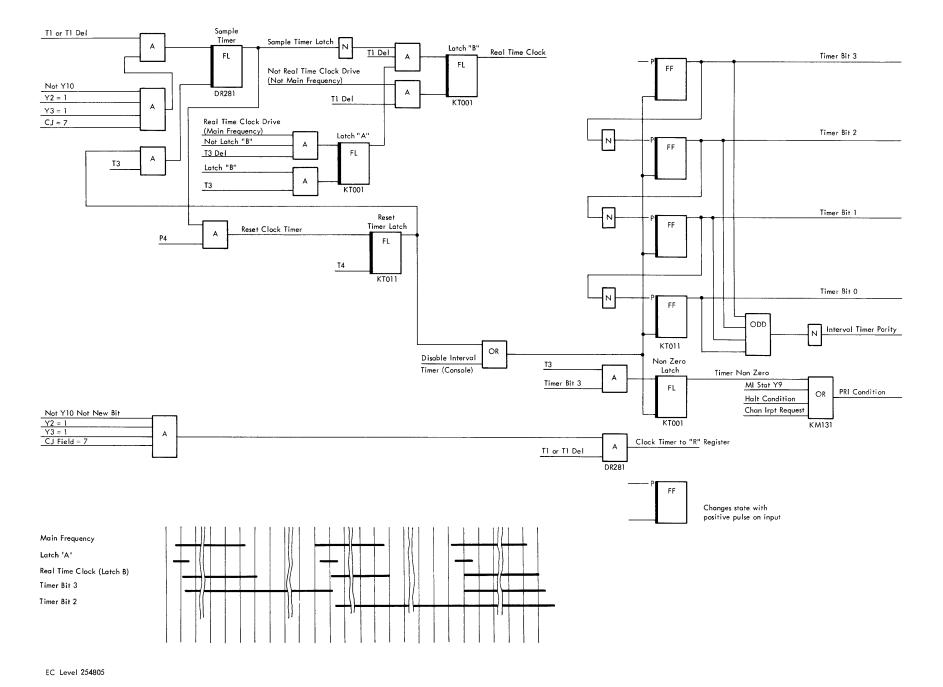

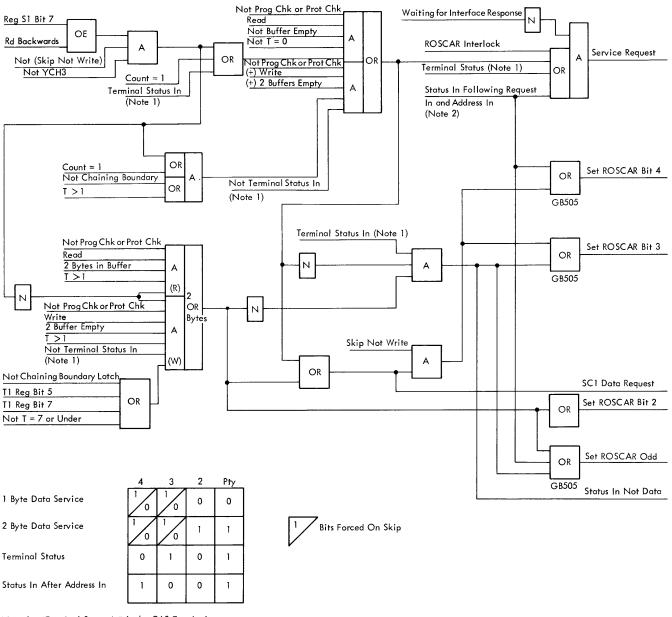

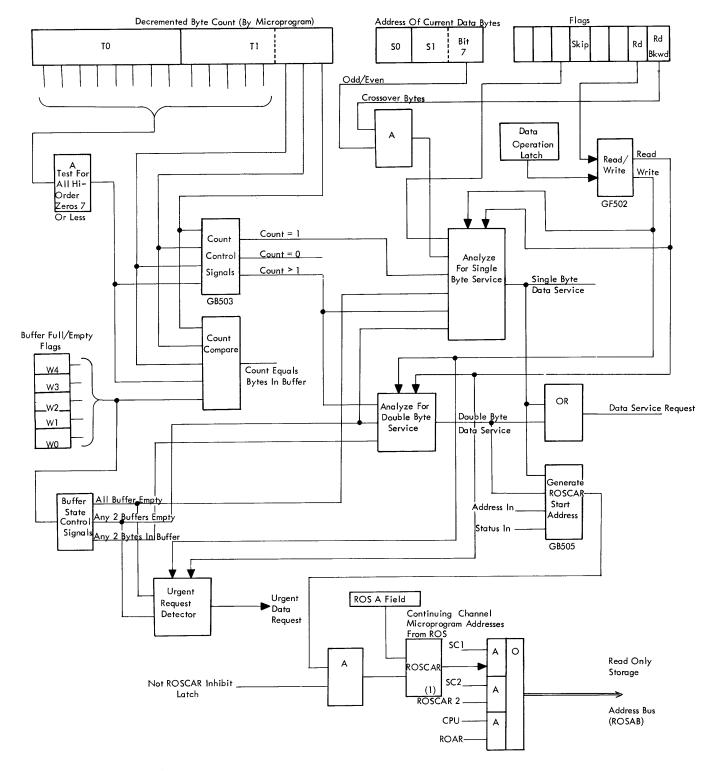

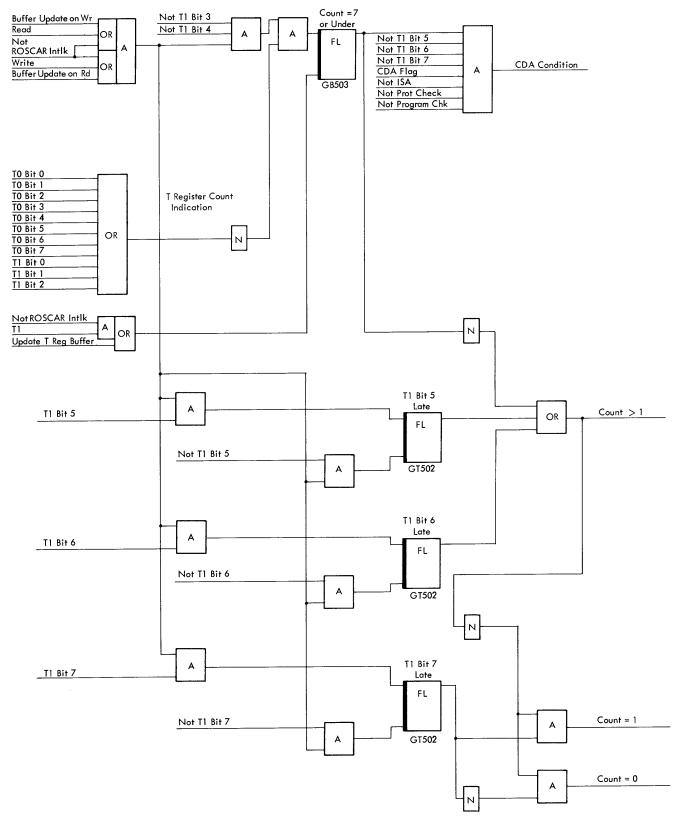

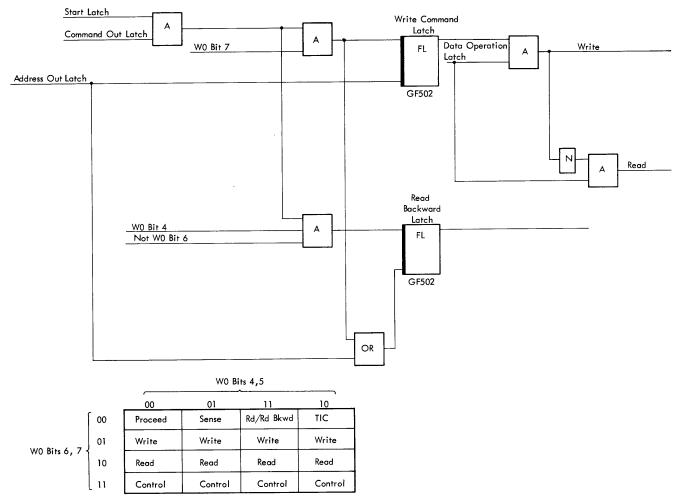

|                    | 12            | Real-Time Clock and Interval Timer          |      | - 1              | 43     | Data Servicing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

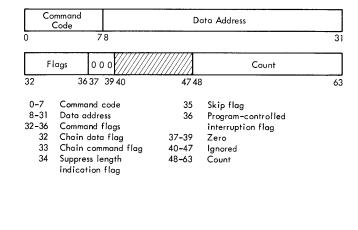

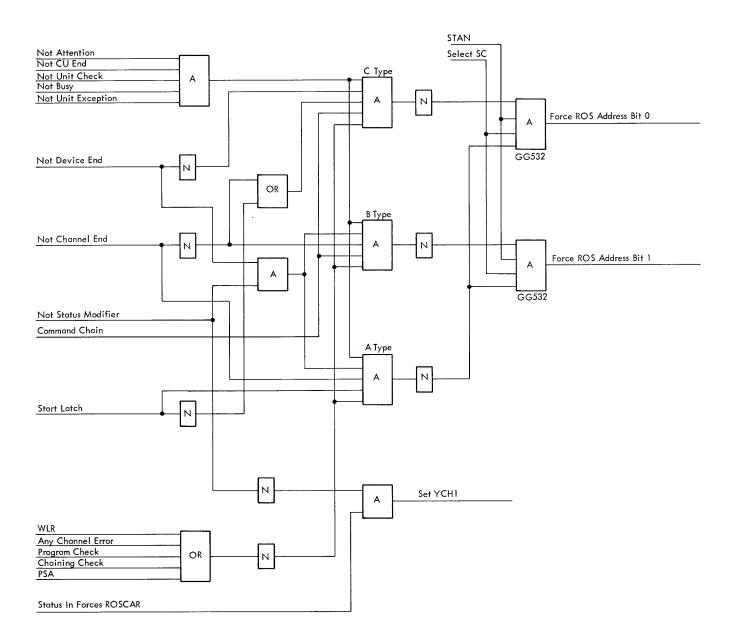

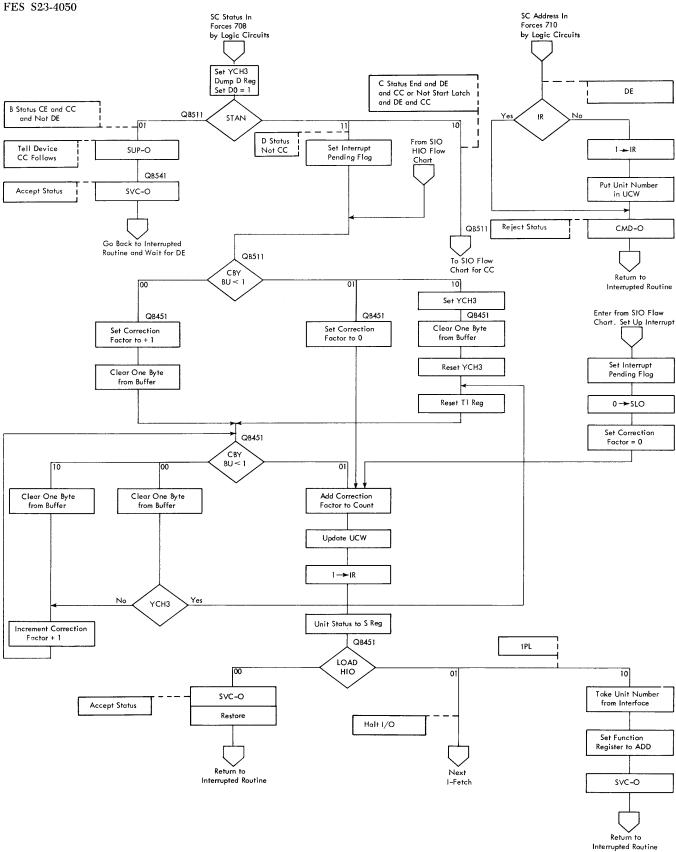

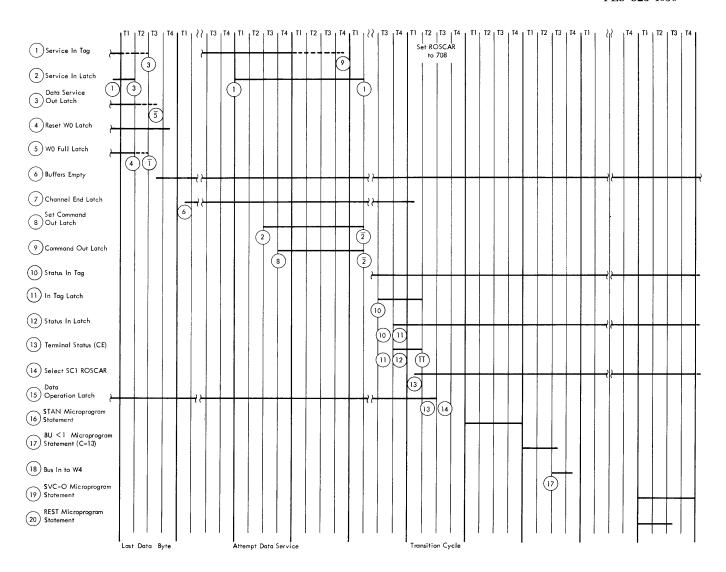

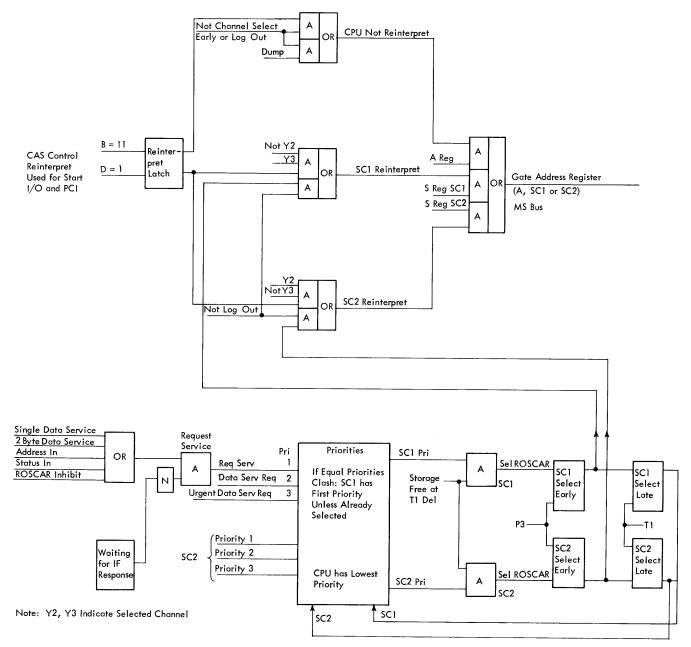

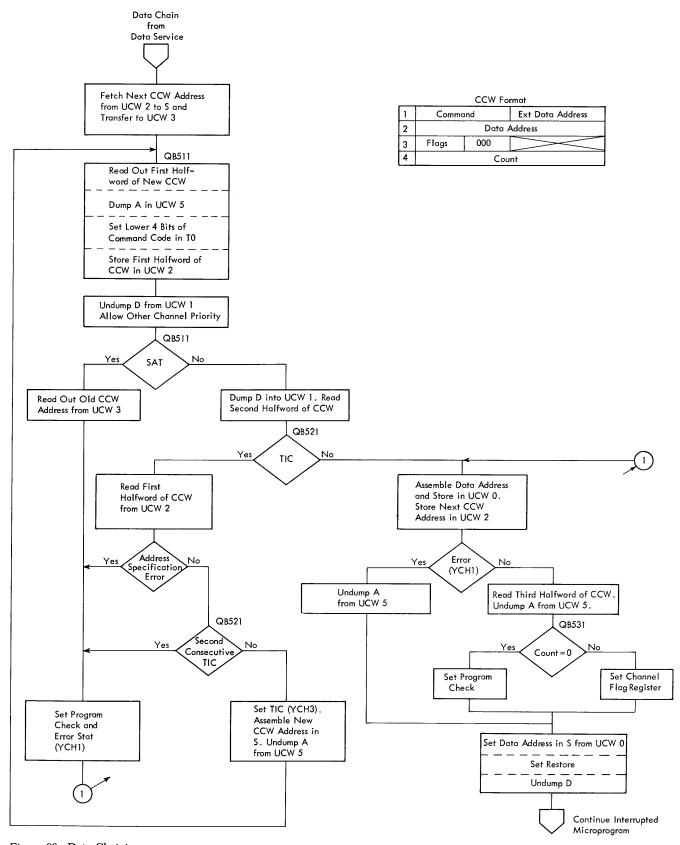

|                    | 13            | Word Formats                                |      | •                | 44     | Status Type Analysis (STAN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

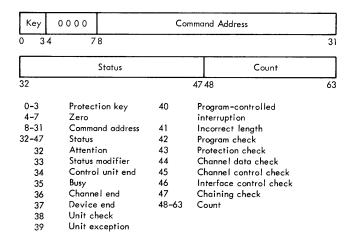

|                    | 14            | Multiplex Channel UCW Format                |      | •                | 45     | Buffer Timing—Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

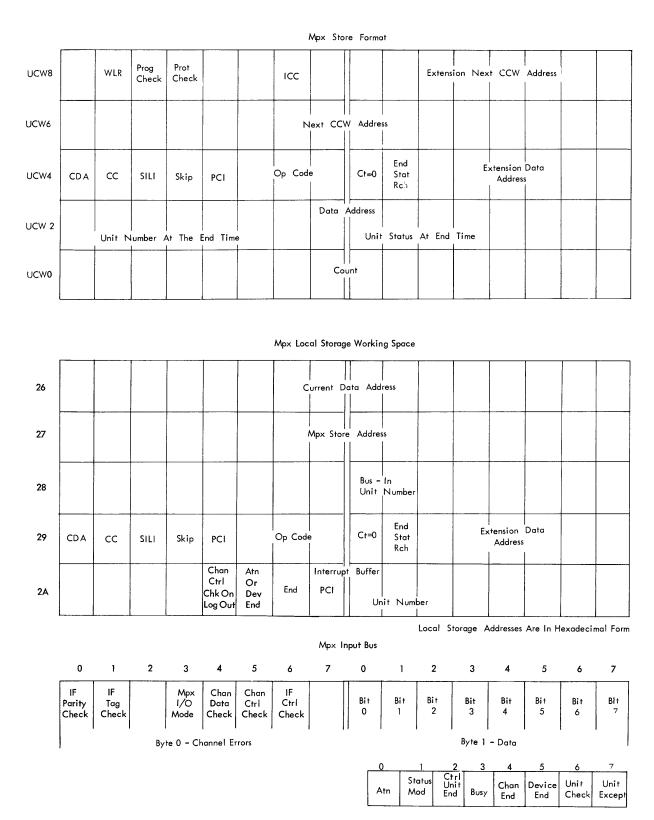

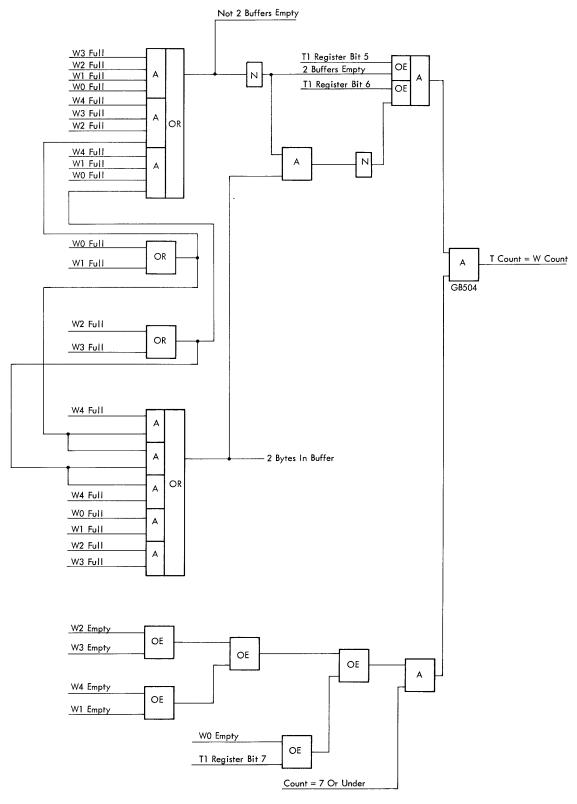

| 1                  | 15            | Multiplex Storage                           | . 31 | •                | 46     | T = W Compare 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

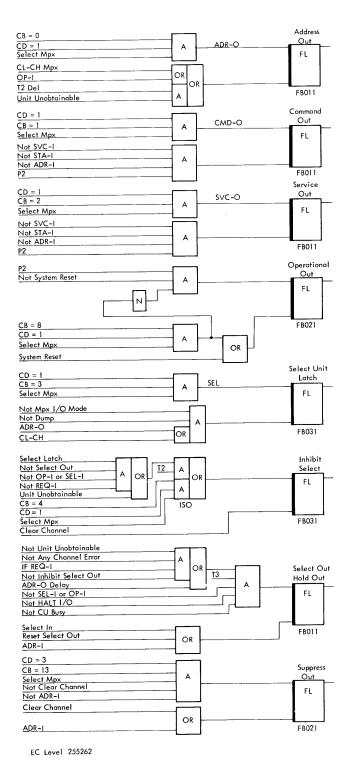

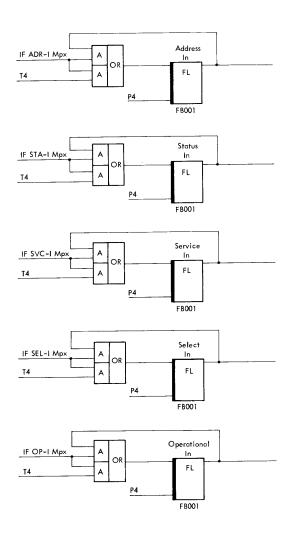

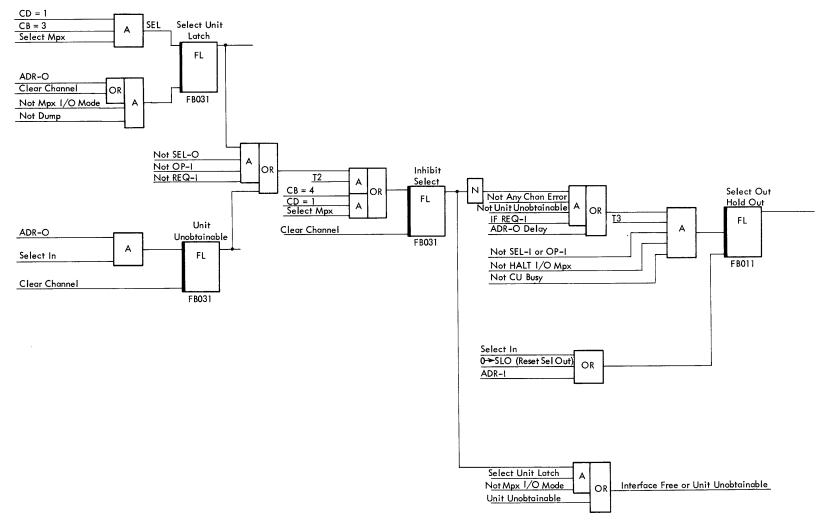

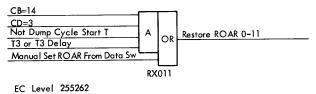

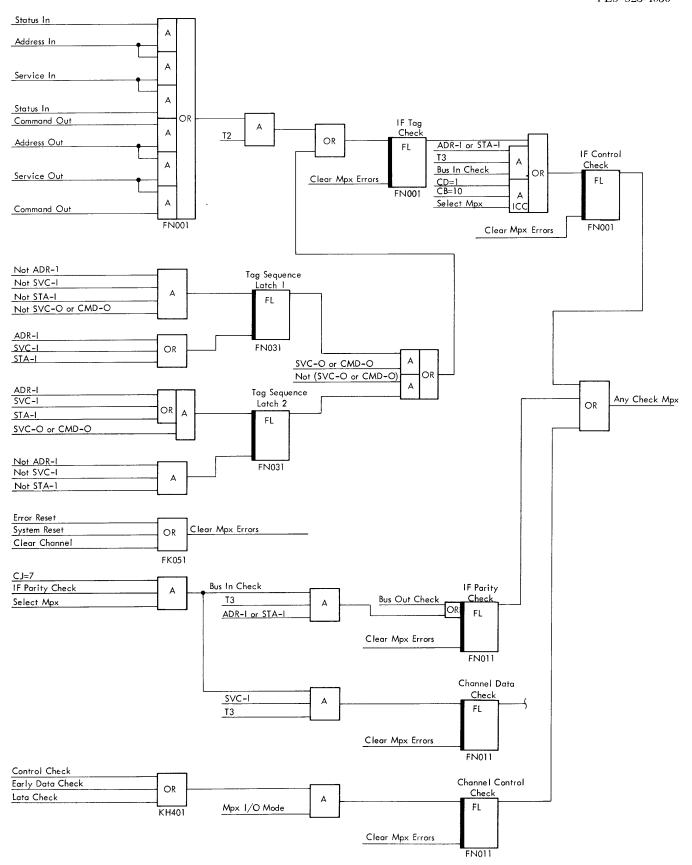

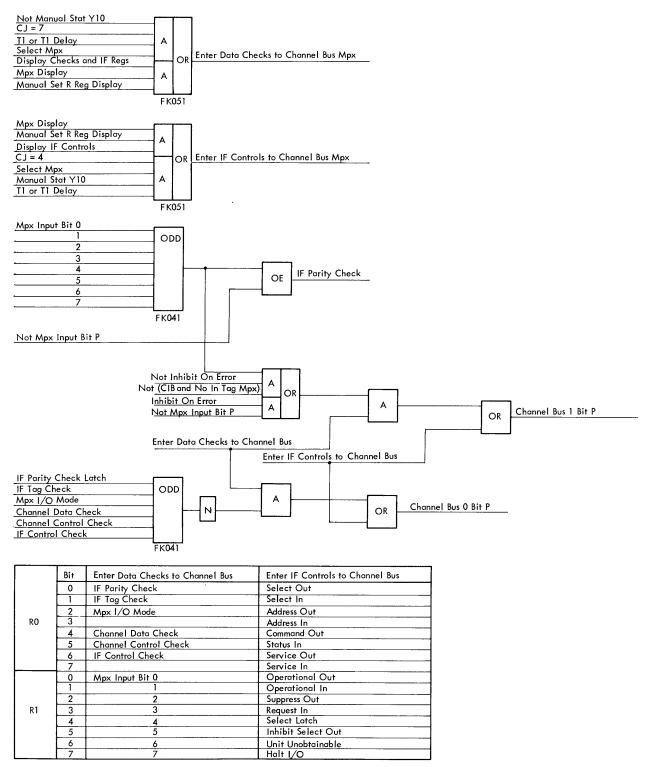

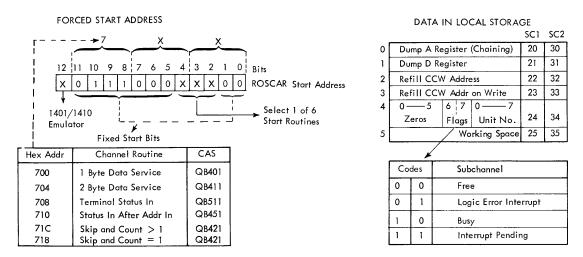

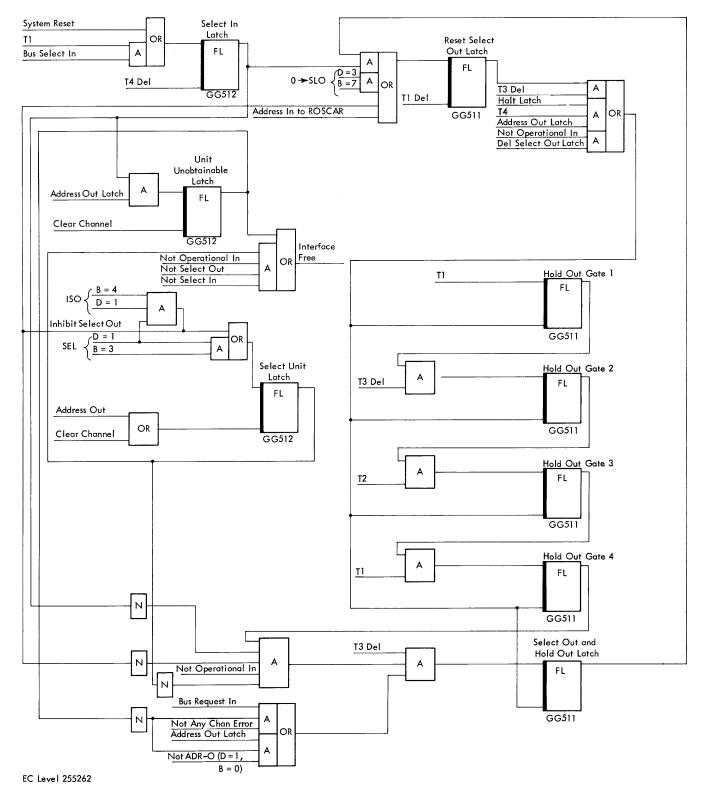

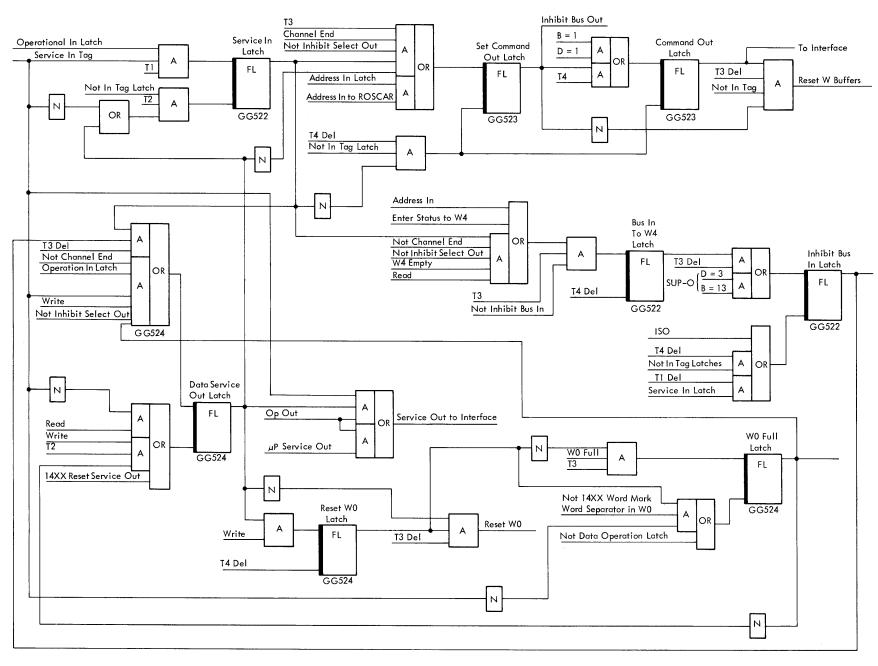

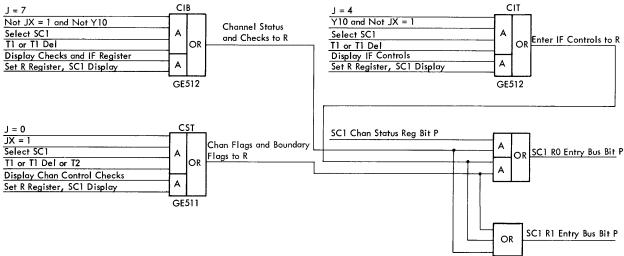

|                    | 16            | Interface Logic-Multiplex Channel           | . 33 |                  |        | 1 W Compare with the second se |  |  |

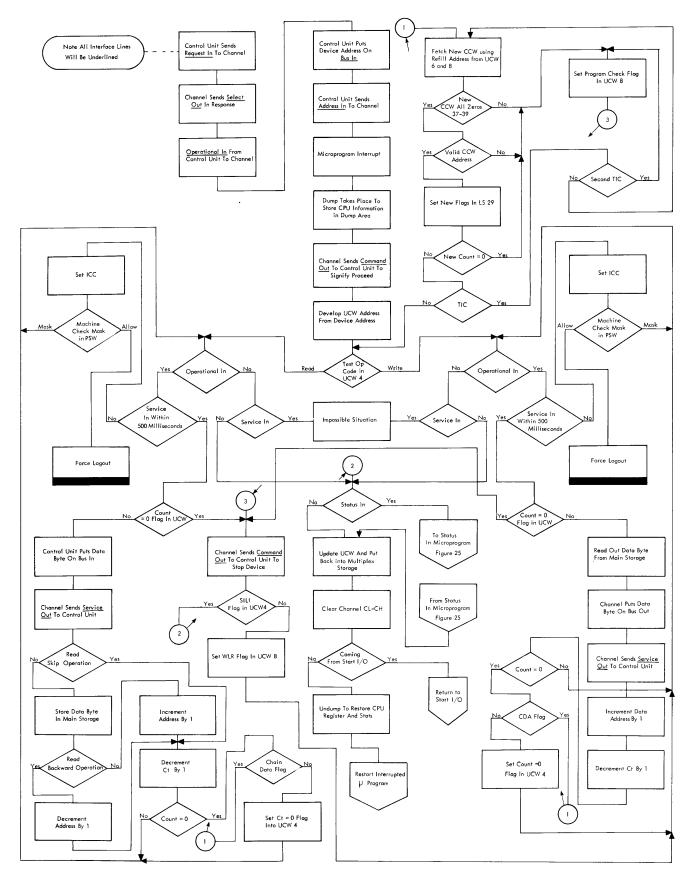

|                    | 17            | Multiplex Channel Normal Operation          | 0=   |                  | 47     | Butte Service Itequest und 1110 11111111111111111111111111111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|                    |               | (Sheet 1 of 2)                              | . 35 |                  | 48     | Country Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                    | 17            | Multiplex Channel Normal Operation          | 20   |                  | 49     | Count Controls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                    | 10            | (Sheet 2 of 2)                              |      |                  | 50     | Channel R/W and Rd/Rd Backward Flags 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

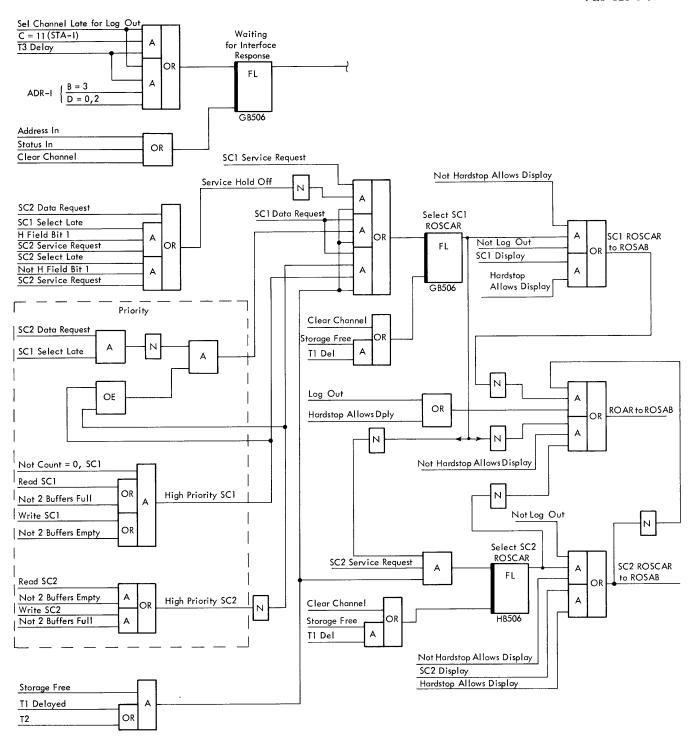

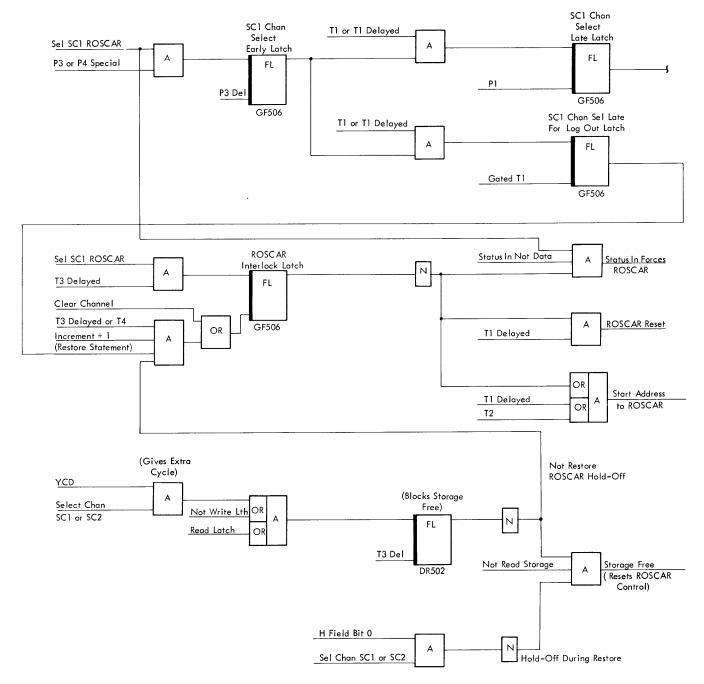

|                    | 18            | Test Channel                                |      | - 1              | 51     | Channel Priorities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 1                  | 19<br>19.1    | Multiplex Unit Selection                    |      | ı                | 52     | Channel Select Latches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

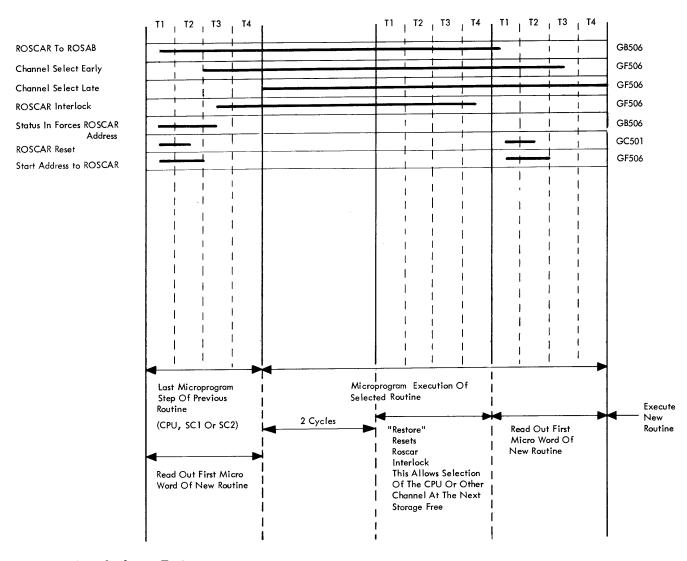

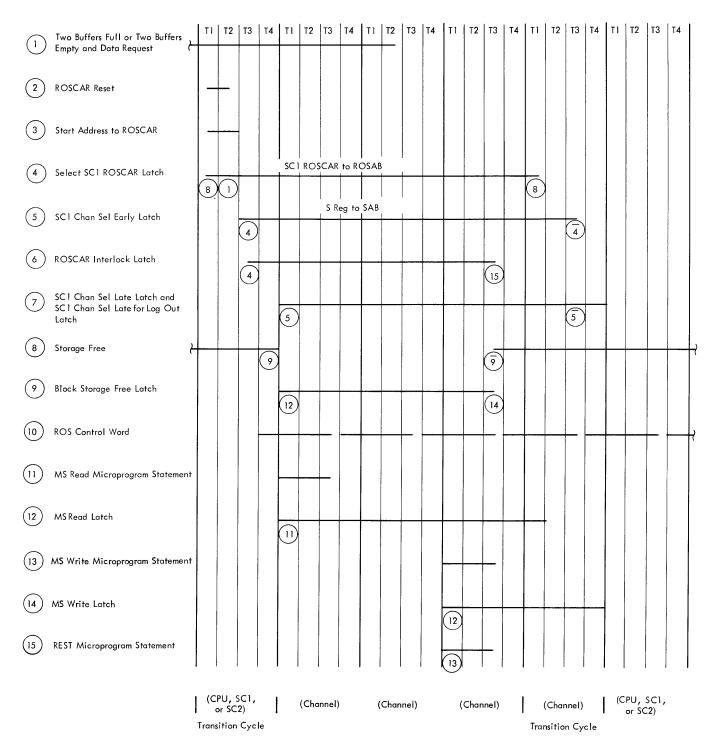

|                    | 20            | Test I/O Mpx Channel                        |      |                  | 53     | Channel Selection Timing 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| ı                  | 21            | Halt I/O Mpx Channel                        |      | ı                | 53.1   | Selector Channel Data Service 97.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

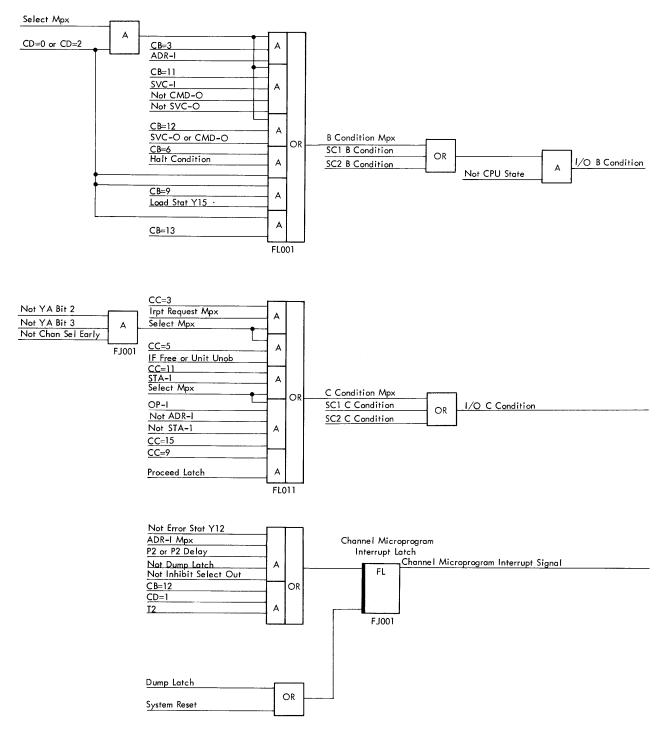

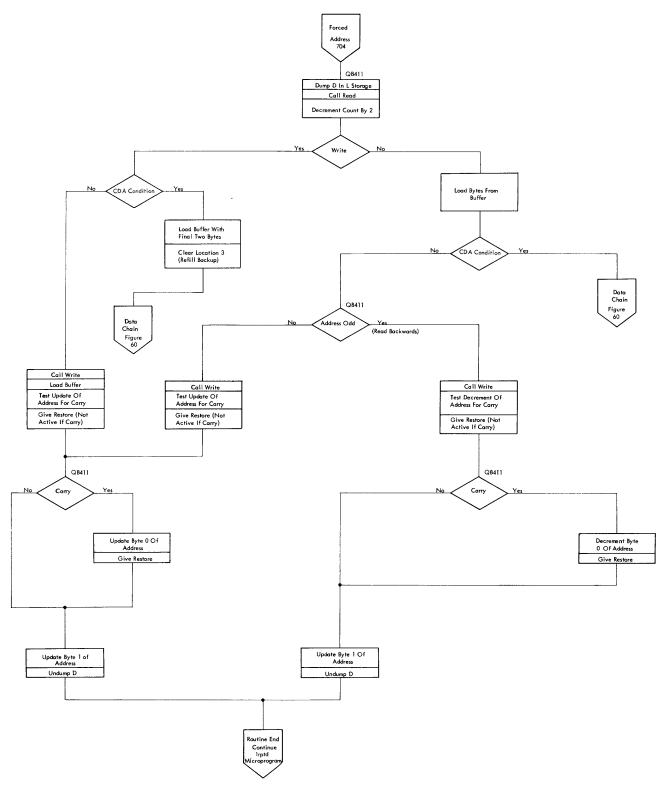

| •                  | 22            | I/O B and C Conditions—Microprogram Interru |      |                  | 54     | Two-Byte Data Service 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

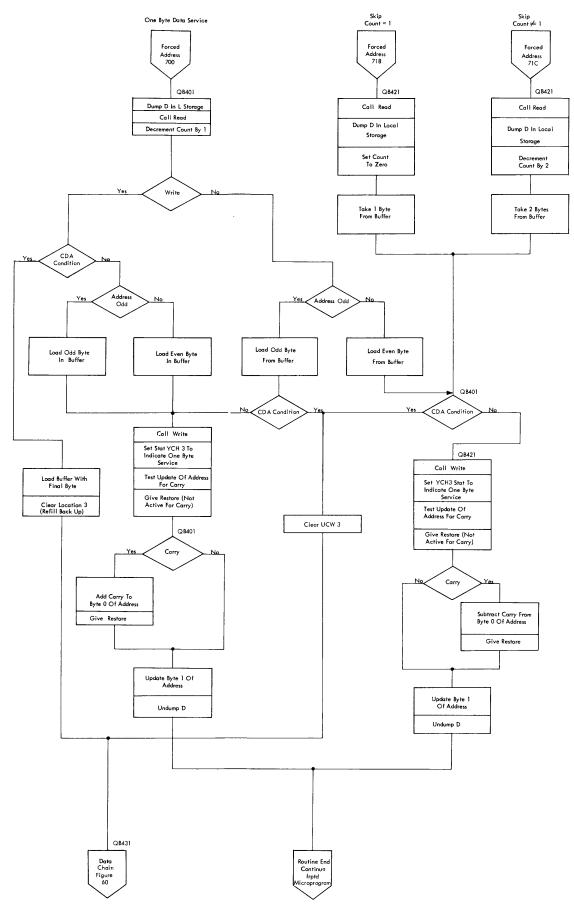

|                    | 23            | Dump and Undump                             |      |                  | 55     | One-Byte Data Service and Skip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

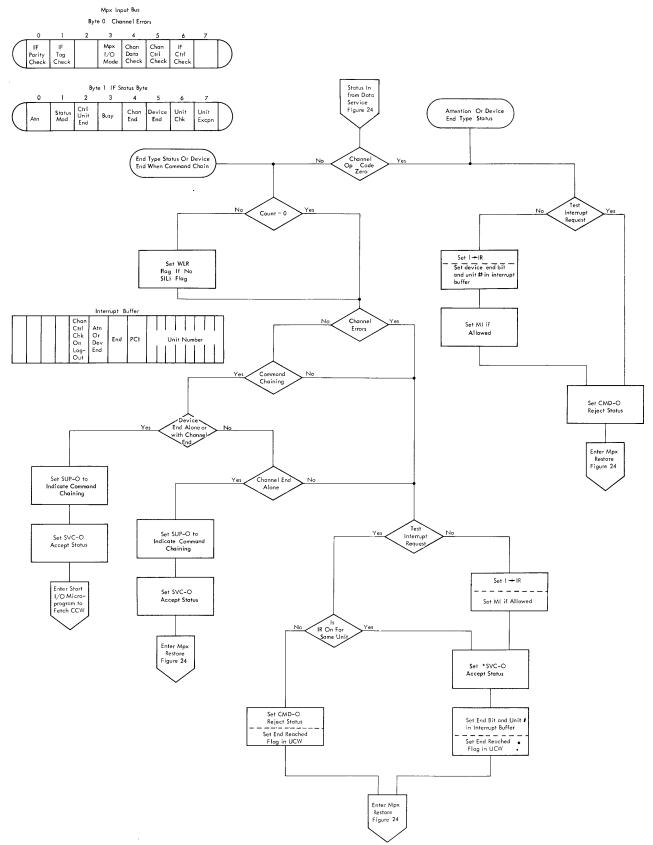

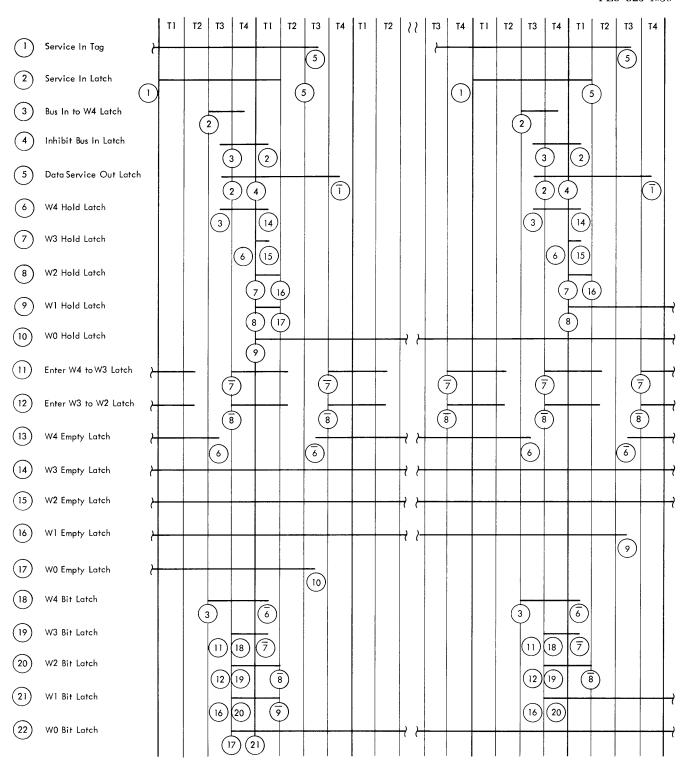

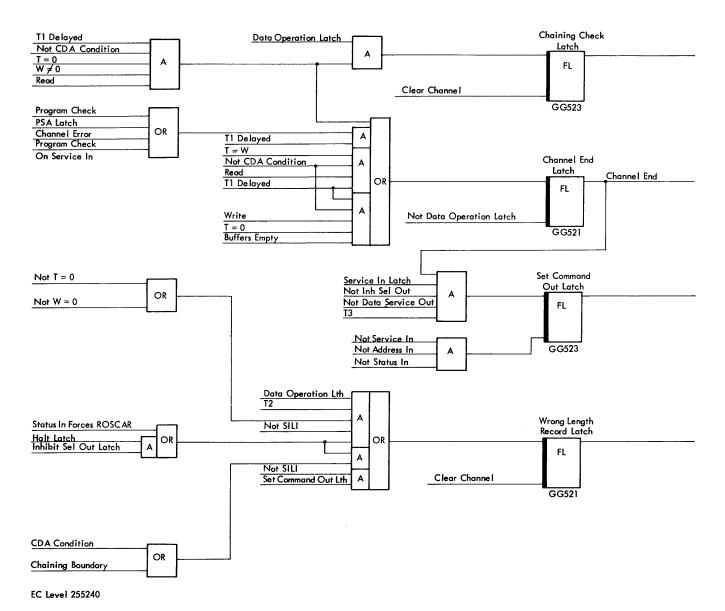

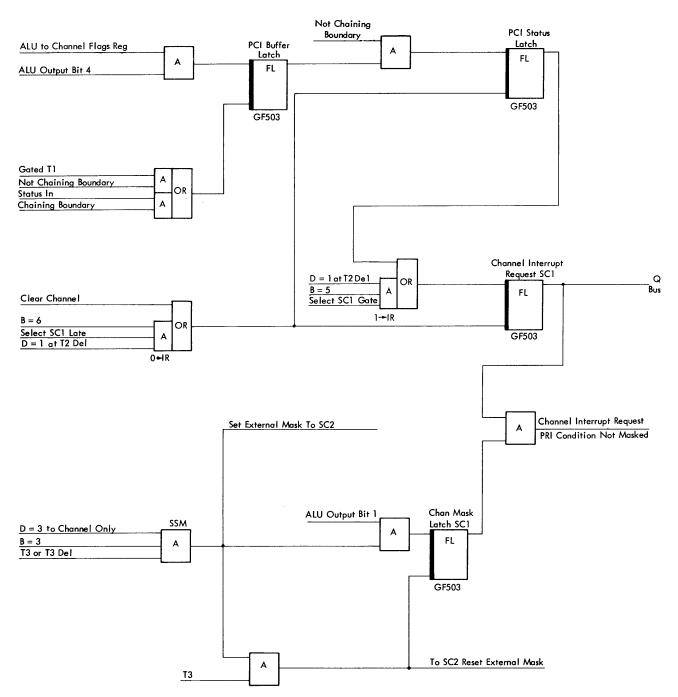

|                    | 24            | Multiplex Data Service                      |      |                  | 56     | Channel End-Wrong Length Record Latches 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |